## Nios® II + UART Project on Intel® MAX® 10-10M08 Evaluation Kit

By Sean D. Liming and John R. Malin Annabooks, LLC. – <u>www.annabooks.com</u>

December 2022

This hands-on article will walk through the creation of a couple of Nios II + UART designs. We will explore some tool features along the way.

Please, see the <u>article Intel® Quartus® Prime Lite and Nios® II SBT for Eclipse Installation</u> <u>Instructions</u> on Annabooks.com for information on how to install the software needed for this handson exercise.

The Project Requirements:

- Intel Quartus Prime Lite Edition V21.0 and Nios® II SBT for Eclipse are already installed.

- Intel® MAX® 10 10M08 Evaluation Kit and the schematic for the evaluation board are required. The schematic PDF file can be downloaded from the Intel FPGA website.

- Intel FPGA Programming cable USB Blaster II or EthernetBlaster II. The Intel® MAX® 10 - 10M08 Evaluation Kit doesn't have a built-in USB Blaster II onboard.

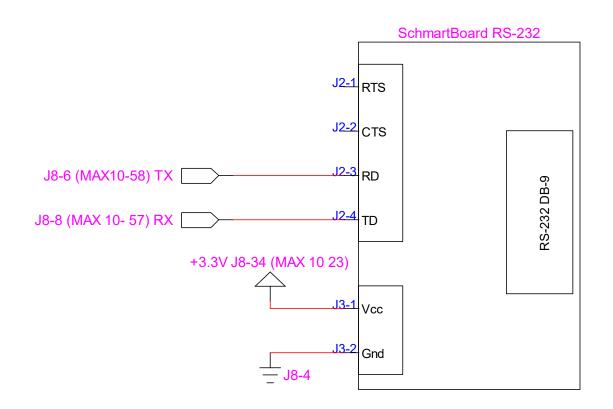

- SchmartBoard RS-232 to UART board: <u>RS-232 I/O Module | Schmartboard.</u> An RS-232 transceiver chip is needed to convert the RX and TX digital signals to the expected RS-232 signals.

- Serial null modem cable.

- RS-232-to-USB adapter.

- A terminal program such as ABCOMTerm (<u>www.annabooks.com</u>), HyperTerminal, or Tera Term.

- Optional: SparkFun 16 x 2 matrix Serial LCD with Serial Interface. SparkFun has a few of these LCD displays that support Serial, I2C, and SPI interfaces: <u>SparkFun 16x2 SerLCD –</u> <u>RGB Text (Qwiic) – LCD-16397 – SparkFun Electronics</u>

- Intel® Quartus® Prime Lite and NIOS® II SBT for Eclipse Installation Instructions on Annabooks.com.

**Note**: There are equivalent MAX 10 development and evaluation boards available. These boards can also be used as the target, but you will have to adjust to the available features on the board. Please, make sure that you have the board's schematic files as these will be needed to identify pins.

### 1.1 Simple Nios II UART Project

For this design, an application will run on the Nios II processor to send communications back and forth over a serial cable. There are two parts to the design process: the first involves creating the hardware design in Quartus Prime and Platform Builder, and the second step is to create the application with Eclipse.

#### 1.1.1 Create the Project

The first step is to create the design project.

- 1. Open Quartus.

- 2. Click on the New Project Wizard.

- 3. Click Next to the Introduction dialog.

- 4. Select or create a project directory \NIOS2\_UART (Do not use the Quartus installation directory) and name of the project: "NIOS2uart". Click Next.

**Note**: By default, the root directory is the Quartus installation directory. Make sure the root project directory is a separate path from the Quartus installation files. Also, there can be no spaces in the names of the folders or projects.

- 5. Project Type: Empty project, click Next.

- 6. Add File: no files to add, click Next.

- 7. Family, Device & Board Settings: click the Board tab and select: MAX 10 FPGA 10M08 Evaluation Kit. Click Next.

| Devic | e Board the board/development kit you want to target | t for compila | ation. |            |     |                  |         |      |

|-------|------------------------------------------------------|---------------|--------|------------|-----|------------------|---------|------|

| amil  | y: MAX 10                                            | Ŧ             | Develo | pment Kit: | Any |                  |         | Ŧ    |

| vaila | ble boards:                                          |               |        |            |     |                  |         |      |

|       | Name                                                 | Vers          | ion    | Fami       | ly  | Device           | Vendor  |      |

|       | Arrow MAX 10 DECA                                    | 0.9           |        | MAX 10     |     | 10M50DAF484C6GES | Arrow   | 4976 |

|       | BeMicro MAX 10 FPGA Evaluation Kit                   | 1.0           |        | MAX 10     |     | 10M08DAF484C8GES | Arrow   | 8064 |

|       | MAX 10 DE10 - Lite                                   | 1.0           |        | MAX 10     |     | 10M50DAF484C6GES | Altera  | 4976 |

|       | MAX 10 FPGA 10M08 Evaluation Kit                     | 1.0           |        | MAX 10     |     | 10M08SAE144C8GES | Altera  | 8064 |

|       | MAX 10 FPGA Development Kit                          | 1.0           |        | MAX 10     |     | 10M50DAF256C7G   | Altera  | 4976 |

|       | MAX 10 NEEK                                          | 1.0           |        | MAX 10     |     | 10M50DAF484I7G   | Terasic | 4976 |

|       | Odyssey MAX 10 FPGA Kit                              | 1.0           |        | MAX 10     |     | 10M08SAU169C8GES | Macnica | 8064 |

|       |                                                      |               |        |            |     |                  |         |      |

| 4     |                                                      |               |        |            |     |                  |         | Þ    |

|       | eate top-level design file.                          |               |        |            |     |                  |         |      |

|       | care top teret design me.                            |               |        |            |     |                  |         |      |

- 8. EDA Tools: click Next.

- 9. Summary: click Finish.

**Note**: The actual MAX 10 on our board is the 10M08SAE144C8G, thus it is not an Engineering Sample (ES). The next two steps change the device to the production device. Your experience might be different. These next two optional steps change the device.

10. In the Project Navigator pane on the left, right-click on 10: 10M08SAE144C8GE, and select Device from the context menu.

11. In the Available devices, scroll down and select the 10M08SAE144C8G. Click OK.

| Device               | Board            |                                                                   |             |                    |                          |                      |           |                                               |  |

|----------------------|------------------|-------------------------------------------------------------------|-------------|--------------------|--------------------------|----------------------|-----------|-----------------------------------------------|--|

| /ou can ir           | istall addition  | evice you want to ta<br>al device support v<br>n of the Quartus P | vith the Ir | istall Devices co  |                          |                      |           | efer to the <u>Device Support List</u> webpag |  |

| Device fan           | nily             |                                                                   |             |                    | Show in '                | Available de         | vices' li | st                                            |  |

| <u>F</u> amily:      | MAX 10 (DA       | /DF/DC/SA/SC/SI                                                   | •           | Pac <u>k</u> ag    | Pac <u>k</u> age:        |                      | ¥         |                                               |  |

| Dev <u>i</u> c       | e: All           |                                                                   |             | Pin <u>c</u> ount: |                          | Any 👻                |           |                                               |  |

| arget device         |                  |                                                                   |             |                    | Core sp                  | o <u>e</u> ed grade: | Any       |                                               |  |

| ● <u>S</u> pe        | cific device se  | ted by the Fitter<br>lected in 'Available                         | devices'    | list               | Name f<br>✔ S <u>h</u> o | ilter:<br>w advanced | device    | 25                                            |  |

| O <u>O</u> th        | 20<br>20         |                                                                   |             |                    | <u>D</u> evice an        | nd Pin Optic         | ons       |                                               |  |

| A <u>v</u> ailable ( | devices:<br>Iame | Core Voltage                                                      | LEs         | Total I/Os         | GPIOs                    | Memor                | Dite      | Embedded multiplier 9-bit elem                |  |

| -                    | E144C8G          | 3.3V                                                              | 8064        | 101                | 101                      | 387072               | y Dits    | 48                                            |  |

|                      | E144C8GES        |                                                                   | 8064        | 101                | 101                      | 387072               |           | 48                                            |  |

| 10M085A              | E144I7G          | 3.3V                                                              | 8064        | 101                | 101                      | 387072               |           | 48                                            |  |

| 1000854              | F144I7P          | 3.3V                                                              | 8064        | 101                | 101                      | 387072               |           | 48                                            |  |

|                      |                  |                                                                   |             |                    |                          |                      |           |                                               |  |

#### 1.1.2 Create the Design Step 1: Platform Designer

Now, we will create the platform in Platform Designer.

1. From the menu, select Tools->Platform Designer, or the Platform Designer icon from the toolbar.

The Platform Designer tool is launched. By default, a clock (clk\_0) is added to the design. Platform Designer makes it easy to add IP blocks and make interconnections between the blocks.

2. The top-left pane contains the IP Catalog with all the available IP blocks that come with Quartus Prime. In the search box, type Nios.

| 📂 IP Catalog 🛛 🕅 |                                                                                                                                                                                                                                                           | - 🗗 🗆                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 🔍 NIOS           |                                                                                                                                                                                                                                                           | × 🕸                  |

|                  | ebug and Verification<br>n<br>ios II Custom Instruction<br>eripherals<br>s<br>istom Instructions<br>itswap<br>custom Instruction Interco<br>custom Instruction Master<br>lustom Instruction Slave T<br>loating Point Hardware<br>loating Point Hardware 2 | onnect<br>Translator |

| <                |                                                                                                                                                                                                                                                           | >                    |

| New Edit         |                                                                                                                                                                                                                                                           | ➡ Add                |

- 3. Expand the Processors and Peripherals and Embedded Processors branches and doubleclick on the Nios II Processor

- 4. This will open the Nios II Configuration page. The first tab is used to select the type of core: Nios II/e or Nios II/f. We will keep the defaults for now. Click Finish.

| Nios Il Processor - nios2_gen2_0                                                                                                                                                 |                      |                                                |                                                                                | ×                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------|

| Nios II Processor                                                                                                                                                                |                      |                                                |                                                                                | ·                                     |

| MegaCore altera_1052_genz                                                                                                                                                        |                      |                                                |                                                                                | Documentation                         |

| * Block Diagram                                                                                                                                                                  | Main Vectors         | Caches and Memory Interfaces Arithmetic Instru | ctions MMU and MPU Settings JTAG Debug Adv                                     | vanced Features                       |

| Show signals                                                                                                                                                                     | T Select an I        | nplementation                                  |                                                                                |                                       |

| nios2_gen2_0                                                                                                                                                                     | Nios II Core:        | ○ Nios II/e                                    |                                                                                |                                       |

| cik ckck avaion data_master_                                                                                                                                                     |                      | Nios II/f                                      |                                                                                |                                       |

| reset avaion instruction_master                                                                                                                                                  |                      | Nios II/e                                      | Nios II/f                                                                      |                                       |

| irg interrupt reset debug_reset_request                                                                                                                                          | Summary              | Resource-optimized 32-bit RISC                 | Performance-optimized 32-bit RISC                                              |                                       |

| debug_mem_slave avalon nios_oustorm_instruction custorm_instruction_master                                                                                                       | Features             | JTAG Debug                                     | JTAG Debug                                                                     |                                       |

| atera_niss2_gen2                                                                                                                                                                 |                      | ECC RAM Protection                             | Hardware Multiply/Divide<br>Instruction/Data Caches<br>Tightly-Coupled Masters |                                       |

|                                                                                                                                                                                  |                      |                                                | ECC RAM Protection                                                             |                                       |

|                                                                                                                                                                                  |                      |                                                | External Interrupt Controller<br>Shadow Register Sets                          |                                       |

|                                                                                                                                                                                  |                      |                                                | MPU<br>MMU                                                                     |                                       |

|                                                                                                                                                                                  | RAM Usage            | 2 + Options                                    | 2 + Options                                                                    |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                | · · · · · · · · · · · · · · · · · · · |

| Error: nios2_gen2_0: Instruction Cache is larger than the Instruction Address. Please reduce<br>Error: nios2_gen2_0: Reset slave is not specified. Please select the reset slave | the Instruction Cach | e Size. Current Tag Size is 0                  |                                                                                |                                       |

| Error: nios2_gen2_0: Exception slave is not specified. Please select the exception slave                                                                                         |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                | Cancel Finish                         |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

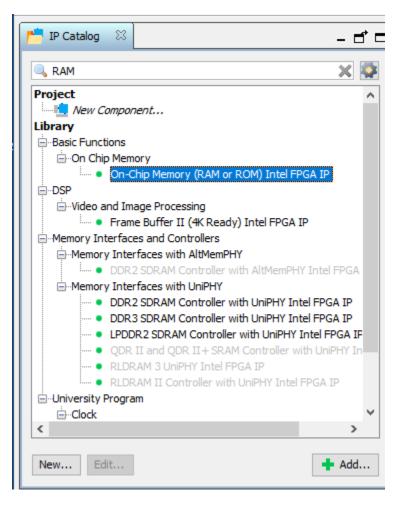

- 5. Now let's add the RAM IP block. In the IP Catalog enter RAM in the search box.

- 6. Double-click on On-chip Memory (RAM or ROM) in the Intel FPGA IP.

7. The configuration page will appear. Change the Total memory size to 16384. We need more memory to run the applications.

| ▼ Size                                   |           |       |

|------------------------------------------|-----------|-------|

| Enable different width for Dual-port acc | tess      |       |

| Slave S1 Data width:                     | 32 🗸      |       |

| Total memory size:                       | 16384     | bytes |

| Minimize memory block usage (may impa    | act fmax) |       |

| Read latency                             |           |       |

8. Uncheck the box for "Initialize memory content", and click Finish.

| Memory initialization                |                                                              |

|--------------------------------------|--------------------------------------------------------------|

| Initialize memory content            |                                                              |

| Enable non-default initialization fi | le                                                           |

| Type the filename (e.g: my_ran       | n.hex) or select the hex file using the file browser button. |

| User created initialization file:    | onchip_mem.hex                                               |

| Enable Partial Reconfiguration Ini   | tialization Mode                                             |

- 9. In the IP Catalog search, enter timer.

- 10. Double-click on the Interval Timer Intel FPGA IP.

| ▶ IP Catalog 🛛               | - 🗗 🗖 |

|------------------------------|-------|

| 🔍 timer                      | ×     |

| Project                      |       |

| Library                      |       |

| -Processors and Peripherals  |       |

| - Peripherals                |       |

| Interval Timer Intel FPGA IP |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

|                              |       |

- 11. Keep the settings as they are and click Finish.

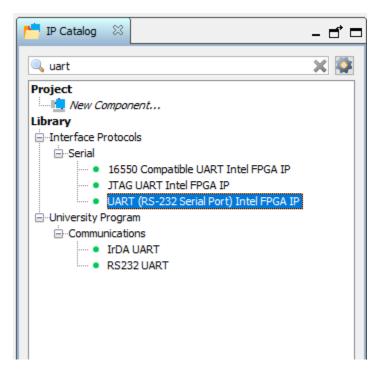

- 12. In the IP Catalog search, enter UART.

- 13. Double-click on the UART (RS-232 Serial Port) Intel FPGA IP16550 Compatible UART Intel FPGA IP.

You will notice that there are two Serial port IPs.16550 Compatible UART Intel FPGA IP and UART (RS-232 Serial Port) Intel FPGA IP. The former contains support for a full FIFO and DMA transfer. The latter that we chose for this design doesn't have a buffer and is a very simplistic character reader. Since the MAX 10 10M08 Evaluation Kit board is limited to internal RAM blocks, the UART (RS-232 Serial Port) Intel FPGA IP makes practical sense to use. The challenge is with the documentation. If you check the details online for the UART (RS-232 Serial Port) Intel FPGA IP, you will see the name 16550 Compatible UART Intel FPGA IP, which is the other serial port IP, but all the information is for the UART (RS-232 Serial Port) Intel FPGA IP. There is an entire paper from Intel talking about the 16550 Compatible UART Intel FPGA IP – ID: 683130 *Embedded peripherals IP User Guide*. The dual information can get a little confusing.

- 14. A configuration page will appear. The default settings of 115200-8-N-1 are fine for this project. No changes need to be made. Click Finish.

- 15. In the IP Catalog search, enter the system ID.

- 16. Double-click on the System ID Peripheral Intel FPGA IP.

17. A configuration page will appear. No changes need to be made. Click Finish.

| i s | System       | Contents 🛛  | Address Ma                | p  | Interconnect Require | ements 🛛                             |

|-----|--------------|-------------|---------------------------|----|----------------------|--------------------------------------|

|     | <b>X</b>     | 🕷 System    | : NIOS2uartC              | PU | Path: sysid_qsys_0   |                                      |

| •   | Use          | Connections |                           | Na | me                   | Description                          |

|     | $\checkmark$ |             |                           |    | clk_0                | Clock Source                         |

| <   |              |             | ⊳-                        | +  | dk_in                | Clock Input                          |

| 2   |              |             | °−                        | +  | dk_in_reset          | Reset Input                          |

|     |              |             |                           |    | dk                   | Clock Output                         |

|     |              |             |                           |    | dk_reset             | Reset Output                         |

|     | $\checkmark$ |             |                           |    | 🖳 nios2_gen2_0       | Nios II Processor                    |

|     |              | ¢           | $\rightarrow$             |    | dk                   | Clock Input                          |

| z   |              |             | $\rightarrow \rightarrow$ |    | reset                | Reset Input                          |

|     |              |             |                           |    | data_master          | Avalon Memory Mapped Master          |

|     |              |             |                           |    | instruction_master   | Avalon Memory Mapped Master          |

|     |              |             | $\rightarrow$             |    | irq                  | Interrupt Receiver                   |

|     |              |             | $\rightarrow$             |    | debug_reset_request  | Reset Output                         |

|     |              | ••          | $\rightarrow$             |    | debug_mem_slave      | Avalon Memory Mapped Slave           |

|     |              |             | ×                         |    | custom_instruction_m | Custom Instruction Master            |

|     | $\checkmark$ |             |                           |    | onchip_memory2_0     | On-Chip Memory (RAM or ROM) Intel .  |

|     |              | ¢           | $\rightarrow$             |    | dk1                  | Clock Input                          |

|     |              |             | $\rightarrow$             |    | s1                   | Avalon Memory Mapped Slave           |

|     |              | ↓ ↓         | $\rightarrow \rightarrow$ |    | reset1               | Reset Input                          |

|     | $\checkmark$ |             |                           |    | timer_0              | Interval Timer Intel FPGA IP         |

|     |              | ¢           | $\rightarrow$             |    | dk                   | Clock Input                          |

|     |              |             | $\rightarrow \rightarrow$ |    | reset                | Reset Input                          |

|     |              |             | $\rightarrow$             |    | s1                   | Avalon Memory Mapped Slave           |

|     |              | <b></b>     |                           |    | irq                  | Interrupt Sender                     |

|     | $\checkmark$ |             |                           |    | uart_0               | UART (RS-232 Serial Port) Intel FPGA |

|     |              | ¢           | $\rightarrow$             |    | dk                   | Clock Input                          |

|     |              |             | $\rightarrow \rightarrow$ |    | reset                | Reset Input                          |

|     |              |             | $\rightarrow$             |    | s1                   | Avalon Memory Mapped Slave           |

|     |              |             | <u>~</u> ~                | ł  | external_connection  | Conduit                              |

|     |              | ○           |                           |    | irq                  | Interrupt Sender                     |

|     | $\checkmark$ |             |                           | Θ  | sysid_qsys_0         | System ID Peripheral Intel FPGA IP   |

|     |              | ¢           | $\rightarrow$             |    | clk                  | Clock Input                          |

|     |              |             | $\rightarrow \rightarrow$ |    | reset                | Reset Input                          |

|     |              | o_o_        | $\rightarrow$             |    | control_slave        | Avalon Memory Mapped Slave           |

18. Now we need to wire the IP blocks together. First, wire all the clk lines together by clicking on the dots for all five IP blocks.

| Use | Connections | Name                 | Description                                       |

|-----|-------------|----------------------|---------------------------------------------------|

|     |             | ⊟ dk_0               | Clock Source                                      |

|     |             |                      | Clock Input                                       |

|     | ,□          |                      | Reset Input                                       |

|     |             | dk dk                | Clock Output                                      |

|     |             | clk_reset            | Reset Output                                      |

|     |             | ⊡ 🖳 nios2_gen2_0     | Nios II Processor                                 |

|     | <b>+</b>    | ) dk                 | Clock Input                                       |

|     | ↓           | reset                | Reset Input                                       |

|     |             | data_master          | Avalon Memory Mapped Master                       |

|     |             | instruction_master   | Avalon Memory Mapped Master                       |

|     |             | irq                  | Interrupt Receiver                                |

|     |             | debug_reset_request  | Reset Output                                      |

|     |             | debug_mem_slave      | Avalon Memory Mapped Slave                        |

|     | ×           | custom_instruction_m | . Custom Instruction Master                       |

|     |             | onchip_memory2_0     | On-Chip Memory (RAM or ROM) Inte                  |

|     |             | dk1                  | Clock Input                                       |

|     |             | s1                   | Avalon Memory Mapped Slave                        |

| _   |             | reset1               | Reset Input                                       |

|     |             | ⊡ timer_0            | Interval Timer Intel FPGA IP                      |

|     |             | + dk                 | Clock Input                                       |

|     |             | reset                | Reset Input                                       |

|     |             | s1                   | Avalon Memory Mapped Slave                        |

|     | ¢           | irq                  | Interrupt Sender                                  |

|     |             | □ uart_0             | UART (RS-232 Serial Port) Intel FPG/              |

|     |             | + dk                 | Clock Input                                       |

|     |             | reset                | Reset Input                                       |

|     |             | s1                   | Avalon Memory Mapped Slave                        |

|     |             |                      | Conduit                                           |

|     |             |                      | Interrupt Sender                                  |

|     |             | ☐ sysid_qsys_0 dk    | System ID Peripheral Intel FPGA IP<br>Clock Input |

|     |             | reset                | Reset Input                                       |

|     |             | control_slave        | Avalon Memory Mapped Slave                        |

19. Next, connect all the reset lines together by clicking on the dots for all five IP blocks.

| l | <b>X</b>     | System:               |                           |                            |                                           |

|---|--------------|-----------------------|---------------------------|----------------------------|-------------------------------------------|

| 5 |              | 1 10000               | NIOS2uartCF               | PU Path: sysid_qsys_0.rese | t                                         |

| 8 | Use          | Connections           |                           | Name                       | Description                               |

|   |              |                       |                           | □ clk_0                    | Clock Source                              |

|   |              |                       | ⊳                         | clk_in                     | Clock Input                               |

|   |              |                       | ·                         | dk_in_reset                | Reset Input                               |

|   |              |                       |                           | dk                         | Clock Output                              |

|   |              |                       |                           | clk_reset                  | Reset Output                              |

| • | $\checkmark$ |                       |                           | 曰 喧 nios2_gen2_0           | Nios II Processor                         |

| - |              | <b>+ 1</b>            | $\rightarrow$             | clk                        | Clock Input                               |

| : |              | +                     | $\rightarrow \rightarrow$ | reset                      | Reset Input                               |

|   |              |                       |                           | data_master                | Avalon Memory Mapped Master               |

|   |              |                       |                           | instruction_master         | Avalon Memory Mapped Master               |

|   |              |                       | $\rightarrow$             | irq                        | Interrupt Receiver                        |

|   |              |                       | <b>`</b>                  | debug_reset_request        | Reset Output                              |

|   |              | │┃┿┿┼                 | $\rightarrow$             | debug_mem_slave            | Avalon Memory Mapped Slave                |

|   |              |                       | ×                         | custom_instruction_m       | Custom Instruction Master                 |

|   |              |                       |                           | onchip_memory2_0           | On-Chip Memory (RAM or ROM) Intel .       |

|   |              | •                     | $\rightarrow$             | dk1                        | Clock Input                               |

|   |              |                       | $\rightarrow$             | s1                         | Avalon Memory Mapped Slave                |

|   |              |                       | $\rightarrow$             | reset1                     | Reset Input                               |

|   | $\square$    |                       |                           | ⊡ timer_0                  | Interval Timer Intel FPGA IP              |

|   |              | <b>†</b>              | $\rightarrow$             | clk                        | Clock Input                               |

|   |              |                       | $\uparrow \rightarrow$    | reset                      | Reset Input                               |

|   |              | $\diamond \diamond +$ | $\rightarrow$             | s1                         | Avalon Memory Mapped Slave                |

|   | _            |                       |                           | irq                        | Interrupt Sender                          |

|   |              |                       |                           | □ uart_0                   | UART (RS-232 Serial Port) Intel FPGA I    |

|   |              | •                     | $\rightarrow$             | dk                         | Clock Input                               |

|   |              |                       |                           | reset                      | Reset Input                               |

|   |              |                       |                           | s1                         | Avalon Memory Mapped Slave                |

|   |              |                       | 60                        | external_connection        | Conduit                                   |

|   |              | · · · · ·             |                           | irq                        | Interrupt Sender                          |

|   |              |                       |                           | sysid_qsys_0               | System ID Peripheral Intel FPGA IP        |

|   |              | •                     |                           | dk                         | Clock Input                               |

|   |              |                       | *                         | reset<br>control_slave     | Reset Input<br>Avalon Memory Mapped Slave |

20. The memory lines have to be connected together. The s1 line in the RAM is to be connected to the nios2\_gen\_cpu data\_master and instruction master lines. Click on the dots for the RAM s1 line.

|   |              | Contents 🛛  | Address Ma                  |   | Interconnect Require Path: onchip_memory2_0 |                                        |

|---|--------------|-------------|-----------------------------|---|---------------------------------------------|----------------------------------------|

| F | Use          | Connections |                             |   | me                                          | Description                            |

| • |              |             |                             |   |                                             | Clock Source                           |

| × |              |             | ⊳-                          |   | _                                           | Clock Input                            |

|   |              |             | → D-                        |   | -                                           | Reset Input                            |

| 2 |              |             |                             |   |                                             | Clock Output                           |

| • |              | [           |                             |   |                                             | Reset Output                           |

| • |              |             |                             | Ξ | -<br>-                                      | Nios II Processor                      |

| • |              | ↓           | $\rightarrow$               | - | _                                           | Clock Input                            |

| • |              | ↓           | $\rightarrow$ $\rightarrow$ |   |                                             | Reset Input                            |

|   |              | ,           | <b></b>                     |   |                                             | Avalon Memory Mapped Master            |

|   |              |             | <b></b>                     |   | _                                           | Avalon Memory Mapped Master            |

|   |              |             | $\rightarrow$               |   | irq                                         | Interrupt Receiver                     |

|   |              |             | - <del> </del>              |   | debug_reset_request                         | Reset Output                           |

|   |              | + + -       | $\rightarrow$               |   | debug_mem_slave                             | Avalon Memory Mapped Slave             |

|   |              |             | - ×                         |   | custom_instruction_m                        | Custom Instruction Master              |

|   |              |             |                             |   | onchip_memory2_0                            | On-Chip Memory (RAM or ROM) Intel .    |

|   |              | •           | $\rightarrow$               |   | dk1                                         | Clock Input                            |

|   |              | ▏▏▕╇╼╇╼┥    | $\rightarrow$               |   | s1                                          | Avalon Memory Mapped Slave             |

|   |              | •           | $\rightarrow$               |   | reset1                                      | Reset Input                            |

|   | $\checkmark$ |             |                             |   | timer_0                                     | Interval Timer Intel FPGA IP           |

|   |              | •           | $\rightarrow$               |   | dk                                          | Clock Input                            |

|   |              | +           | $\rightarrow \rightarrow$   |   | reset                                       | Reset Input                            |

|   |              |             | $\rightarrow$               |   | s1                                          | Avalon Memory Mapped Slave             |

|   |              | ¢           |                             |   |                                             | Interrupt Sender                       |

|   |              |             |                             |   | _                                           | UART (RS-232 Serial Port) Intel FPGA I |

|   |              | •           | $\rightarrow$               |   |                                             | Clock Input                            |

|   |              |             | $\rightarrow \rightarrow$   |   |                                             | Reset Input                            |

|   |              |             | $\rightarrow$               |   |                                             | Avalon Memory Mapped Slave             |

|   |              |             |                             | t | external_connection                         | Conduit                                |

|   |              | 0           | ×                           |   | -                                           | Interrupt Sender                       |

|   |              |             |                             |   |                                             | System ID Peripheral Intel FPGA IP     |

|   |              |             | $\rightarrow$               |   |                                             | Clock Input                            |

|   |              |             | $\rightarrow$               |   |                                             | Reset Input                            |

|   |              | o_>_        | $\rightarrow$               |   | control_slave                               | Avalon Memory Mapped Slave             |

21. Connect Uart\_0's s1 line, time\_0 s1 line, and sysid\_qsys\_0's control\_slave to the nios2\_gen2\_cpu's data\_master.

| <u>i</u> | System (     | Contents 🛛                            | Address Ma                    | p 💠 Interconnect Require   | ements 🛛                               |

|----------|--------------|---------------------------------------|-------------------------------|----------------------------|----------------------------------------|

|          | ∞ ▲          | System:                               | NIOS2uartCF                   | PU Path: sysid_qsys_0.cont | rol_slave                              |

| +        | Use          | Connections                           |                               | Name                       | Description                            |

| -        |              |                                       |                               | ⊡ clk_0                    | Clock Source                           |

| $\times$ |              |                                       | ⊳-                            | clk_in                     | Clock Input                            |

| 2        |              |                                       | <u>о</u> – – – –              | dk_in_reset                | Reset Input                            |

| _        |              |                                       |                               | clk                        | Clock Output                           |

| <b>T</b> |              |                                       |                               | dk_reset                   | Reset Output                           |

| ^        | $\checkmark$ |                                       |                               | 回咀 nios2_gen2_0            | Nios II Processor                      |

| •        |              | •                                     | $\rightarrow$                 | clk                        | Clock Input                            |

| x        |              |                                       | $\leftrightarrow \rightarrow$ | reset                      | Reset Input                            |

|          |              |                                       |                               | data_master                | Avalon Memory Mapped Master            |

|          |              |                                       |                               | instruction_master         | Avalon Memory Mapped Master            |

|          |              |                                       | $\rightarrow$                 | irq                        | Interrupt Receiver                     |

|          |              |                                       | $\rightarrow$                 | debug_reset_request        | Reset Output                           |

|          |              | + + -                                 | $\rightarrow$                 | debug_mem_slave            | Avalon Memory Mapped Slave             |

|          |              |                                       | ×                             | custom_instruction_m       | Custom Instruction Master              |

|          |              |                                       |                               | onchip_memory2_0           | On-Chip Memory (RAM or ROM) Intel      |

|          |              | •                                     | $\rightarrow$                 | dk1                        | Clock Input                            |

|          |              | ││╋╇┼                                 | $\rightarrow$                 | s1                         | Avalon Memory Mapped Slave             |

|          |              | + 1                                   | $\rightarrow \rightarrow$     | reset1                     | Reset Input                            |

|          | $\checkmark$ |                                       |                               | ⊡ timer_0                  | Interval Timer Intel FPGA IP           |

|          |              | • • • • • • • • • • • • • • • • • • • | $\rightarrow$                 | clk                        | Clock Input                            |

|          |              | + 1                                   | $\rightarrow \rightarrow$     | reset                      | Reset Input                            |

|          |              | 🕇 🔶                                   | $\rightarrow$                 | s1                         | Avalon Memory Mapped Slave             |

|          |              | ¢                                     |                               | irq                        | Interrupt Sender                       |

|          |              |                                       |                               | 🗆 uart_0                   | UART (RS-232 Serial Port) Intel FPGA I |

|          |              | • • • • • • • • • • • • • • • • • • • | $\rightarrow$                 | clk                        | Clock Input                            |

|          |              |                                       | $\rightarrow$                 | reset                      | Reset Input                            |

|          |              |                                       | $\rightarrow$                 | s1                         | Avalon Memory Mapped Slave             |

|          |              |                                       | P-0-                          | external_connection        | Conduit                                |

|          |              | ♦                                     |                               | irq                        | Interrupt Sender                       |

|          | $\checkmark$ |                                       |                               | sysid_qsys_0               | System ID Peripheral Intel FPGA IP     |

|          |              | •       -                             | $\rightarrow$                 | clk                        | Clock Input                            |

|          |              | •                                     | $\rightarrow$                 | reset                      | Reset Input                            |

|          |              |                                       | $\longrightarrow$             | control_slave              | Avalon Memory Mapped Slave             |

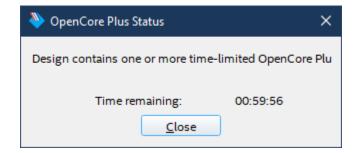

22. Connect uart\_0's irq line and timer\_0's irq to nios2\_gen2\_0 irq.

| <b>1</b> 23 | System (     | Contents 🛛 🛛 🕅 Address Ma                                                                                                                  | p 💠 Interconnect Require   | ements 🛛                               |

|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------|

|             | *            | System: NIOS2uartC                                                                                                                         | PU <b>Path:</b> uart_0.irq |                                        |

| ٠.          | Use          | Connections                                                                                                                                | Name                       | Description                            |

| ۰.          |              |                                                                                                                                            | ⊡ clk_0                    | Clock Source                           |

| X           |              | ⊳-                                                                                                                                         | dk_in                      | Clock Input                            |

| 7           |              | °−D-                                                                                                                                       | dk_in_reset                | Reset Input                            |

|             |              | X                                                                                                                                          | clk                        | Clock Output                           |

| Ξ.          |              |                                                                                                                                            | dk_reset                   | Reset Output                           |

| ٠.          | $\checkmark$ |                                                                                                                                            | 🗆 🛄 nios2_gen2_0           | Nios II Processor                      |

| •           |              | $  \bullet   \longrightarrow$                                                                                                              | clk                        | Clock Input                            |

| T           |              | $    \rightarrow \rightarrow$                                                                                                              | reset                      | Reset Input                            |

|             |              |                                                                                                                                            | data_master                | Avalon Memory Mapped Master            |

|             |              |                                                                                                                                            | instruction_master         | Avalon Memory Mapped Master            |

|             |              | $       \downarrow                              $                                                                                          | irq                        | Interrupt Receiver                     |

|             |              |                                                                                                                                            | debug_reset_request        | Reset Output                           |

|             |              | │ │ <b>♦ <del>♦</del> ┨ ├───→</b>                                                                                                          | debug_mem_slave            | Avalon Memory Mapped Slave             |

|             |              |                                                                                                                                            | custom_instruction_m       | Custom Instruction Master              |

|             |              |                                                                                                                                            | onchip_memory2_0           | On-Chip Memory (RAM or ROM) Intel .    |

|             |              | $  \bullet   + + + + + \rightarrow$                                                                                                        | clk1                       | Clock Input                            |

|             |              | $     \bullet \bullet I \longrightarrow$                                                                                                   | s1                         | Avalon Memory Mapped Slave             |

|             |              | $   + + + + + \rightarrow$                                                                                                                 | reset1                     | Reset Input                            |

|             | $\checkmark$ |                                                                                                                                            | 🗆 timer_0                  | Interval Timer Intel FPGA IP           |

|             |              | $  \bullet   + + + + \rightarrow$                                                                                                          | clk                        | Clock Input                            |

|             |              | $   \bullet   + \bullet \rightarrow$                                                                                                       | reset                      | Reset Input                            |

|             |              | $      \bullet \bullet   \longrightarrow$                                                                                                  | s1                         | Avalon Memory Mapped Slave             |

|             |              |                                                                                                                                            | irq                        | Interrupt Sender                       |

|             |              |                                                                                                                                            | 🗆 uart_0                   | UART (RS-232 Serial Port) Intel FPGA I |

|             |              | $  \bullet + + + \bullet $ | clk                        | Clock Input                            |

|             |              | $   + + + + + + \rightarrow \rightarrow$                                                                                                   | reset                      | Reset Input                            |

|             |              | $      \bullet \bullet I \rightarrow$                                                                                                      | s1                         | Avalon Memory Mapped Slave             |

|             |              | P-0-                                                                                                                                       | external_connection        | Conduit                                |

|             |              |                                                                                                                                            | irq                        | Interrupt Sender                       |

|             |              |                                                                                                                                            | sysid_qsys_0               | System ID Peripheral Intel FPGA IP     |

|             |              | $ \bullet_{\downarrow}  \longrightarrow$                                                                                                   | clk                        | Clock Input                            |

|             |              | $\bullet$                                                                                                                                  | reset                      | Reset Input                            |

|             |              | $\bullet \circ \longrightarrow$                                                                                                            | control_slave              | Avalon Memory Mapped Slave             |

23. If you scroll to the right, the irq is given a default value.

|   |     |          |              |                      |                                         | ,                      |        |           |       |        |            |

|---|-----|----------|--------------|----------------------|-----------------------------------------|------------------------|--------|-----------|-------|--------|------------|

|   |     |          | ~            | instruction_master   | Avalon Memory Mapped Master             | Double-click to export | [clk]  |           |       |        |            |

|   |     |          | <b>→</b>     | irg                  | Interrupt Receiver                      | Double-click to export | [clk]  |           | IRQ 0 | IRQ 3  | 1          |

|   |     |          | -            | debug_reset_request  | Reset Output                            | Double-click to export | [clk]  |           |       |        |            |

|   | +-+ |          | >            | debug_mem_slave      | Avalon Memory Mapped Slave              | Double-click to export | [clk]  | in 0x8800 |       | 0x8fff |            |

|   |     | ×        | <            | custom_instruction_m | Custom Instruction Master               | Double-click to export |        |           |       |        |            |

|   |     |          |              | onchip_memory2_0     | On-Chip Memory (RAM or ROM) Intel       |                        |        |           |       |        |            |

| • | •   |          | →            | dk1                  | Clock Input                             | Double-click to export | clk_0  |           |       |        |            |

|   | +-  |          | >            | s1                   | Avalon Memory Mapped Slave              |                        | [clk1] | in 0x4000 |       | 0x7fff |            |

|   | +   | ÷        | ÷            | reset1               | Reset Input                             | Double-click to export | [clk1] |           |       |        |            |

|   |     |          |              | timer_0              | Interval Timer Intel FPGA IP            |                        |        |           |       |        |            |

| • | •   |          | <b>&gt;</b>  | clk                  | Clock Input                             |                        | clk_0  |           |       |        |            |

|   | +   | ¢        | >            | reset                | Reset Input                             |                        | [clk]  |           |       |        |            |

|   | +   | >        | >            | s1                   | Avalon Memory Mapped Slave              | Double-click to export | [clk]  | in 0x9000 |       | 0x901f |            |

|   |     | +        | ~            | irq                  | Interrupt Sender                        | Double-click to export | [clk]  |           |       |        | ≻−Q        |

|   |     |          |              | uart_0               | UART (RS-232 Serial Port) Intel FPGA IP |                        |        |           |       |        |            |

| • | •   |          | )            | clk                  | Clock Input                             |                        | clk_0  |           |       |        |            |

|   | 🛉 🕂 | ÷        | →            | reset                | Reset Input                             |                        | [clk]  |           |       |        |            |

|   | 🕂   | >        | →            | s1                   | Avalon Memory Mapped Slave              | Double-click to export | [clk]  | in 0x9020 |       | 0x903f |            |

|   |     | <u>~</u> | Н            | external_connection  | Conduit                                 | uart_0                 |        |           |       |        |            |

|   |     | •        | <            | irq                  | Interrupt Sender                        | Double-click to export | [clk]  |           |       |        | <b>—</b> 1 |

|   |     |          |              | sysid_qsys_0         | System ID Peripheral Intel FPGA IP      |                        |        |           |       |        |            |

|   |     |          | <del> </del> | dk                   | Clock Taput                             | Double-click to evport | clk 0  | 1         |       | 1      | 1 1        |

24. Let's assign a base address. From the menu, select System->Assign Base Address. This will remove a number of errors from the message box.

| le Edit Sy     | vstem Generate View Tools Help                                              |   |

|----------------|-----------------------------------------------------------------------------|---|

| rin C          | Upgrade IP Cores                                                            | 1 |

| sys            | Assign Base Addresses                                                       |   |

| Projec         | Assign Interrupt Numbers<br>Assign Custom Instruction Opcodes               | + |

| Library<br>Bas | Create Global Reset Network Show System With Platform Designer Interconnect |   |

|                | Remove Dangling Connections                                                 |   |

|                | Import Interface Requirements                                               | - |

You will see the base and end address values change.

17

| and an Court         |                                         |                        |          |                 |        |          |

|----------------------|-----------------------------------------|------------------------|----------|-----------------|--------|----------|

| Name                 | Description                             | Export                 | Clock    | Base            | End    | IR       |

| ⊡ clk_0              | Clock Source                            |                        |          |                 |        |          |

| dk_in                | Clock Input                             | clk                    | exported |                 |        |          |

| dk_in_reset          | Reset Input                             | reset                  |          |                 |        |          |

| clk                  | Clock Output                            | Double-click to export | clk_0    |                 |        |          |

| dk_reset             | Reset Output                            | Double-click to export |          |                 |        |          |

| 🗆 🛄 nios2_gen2_0     | Nios II Processor                       |                        |          |                 |        |          |

| clk                  | Clock Input                             | Double-click to export | clk_0    |                 |        |          |

| reset                | Reset Input                             | Double-click to export | [dk]     |                 |        |          |

| data_master          | Avalon Memory Mapped Master             | Double-click to export | [clk]    |                 |        |          |

| instruction_master   | Avalon Memory Mapped Master             | Double-click to export | [clk]    |                 |        |          |

| irq                  | Interrupt Receiver                      | Double-click to export | [clk]    |                 | IRQ 0  | IRQ 31   |

| debug_reset_request  | Reset Output                            | Double-click to export | [clk]    |                 |        |          |

| debug_mem_slave      | Avalon Memory Mapped Slave              | Double-click to export | [clk]    | <b>■ 0x4800</b> | 0x4fff |          |

| custom_instruction_m | Custom Instruction Master               | Double-click to export |          |                 |        |          |

| onchip_memory2_0     | On-Chip Memory (RAM or ROM) Intel       |                        |          |                 |        |          |

| clk1                 | Clock Input                             | Double-click to export | clk_0    |                 |        |          |

| s1                   | Avalon Memory Mapped Slave              | Double-click to export | [dk1]    |                 | 0x3fff |          |

| reset1               | Reset Input                             | Double-click to export | [clk1]   |                 |        |          |

| 🖃 uart_0             | UART (RS-232 Serial Port) Intel FPGA IP |                        |          |                 |        |          |

| clk                  | Clock Input                             | Double-click to export | clk_0    |                 |        |          |

| reset                | Reset Input                             | Double-click to export | [clk]    |                 |        |          |

| s1                   | Avalon Memory Mapped Slave              | Double-click to export | [clk]    |                 | 0x501f |          |