# Implementing the ADC on Intel® MAX® 10-10M08 Evaluation Kit

By Sean D. Liming and John R. Malin Annabooks, LLC. – www.annabooks.com

October 2022

This hands-on article will create a simple design for the ADC controller that is built into the MAX 10 FPGAs. The Max 10 is used in conjunction with the higher-end Intel FPGA to provide the ADC support that these higher-end FPGAs don't support. The MAX 10 -10M08 Evaluation Kit developed by Terasic, Inc, is a very simple development board to help make it easy to get started developing with the Quartus Prime software.

The Project Requirements:

- Intel Quartus Prime Lite Edition V21.0 7zip is required to extract the tar file.

- Intel® MAX® 10 10M08 Evaluation Kit the evaluation kit and the schematic for the evaluation board are required. The schematic PDF file can be downloaded from the Intel FPGA website.

- Optional: a populated 10KΩTrimmer pot for R94 on the schematic, part number 3362P-1-103TLF.

- Intel FPGA Programming cable USB Blaster II or EthernetBlaster II. Unlike other FPGA boards, the MAX 10 -10M08 Evaluation Kit doesn't have a built-in USB Blaster solution; so a separate programming cable is required.

- A signal or function generator some kind an AC signal generator, i.e., BK Precision 4012A or equivalent is required.

**Note**: There are equivalent MAX 10 development and evaluation boards available. These boards can also be used as the target, but you will have to adjust to the available features on the board. Please make sure that you have the board's schematic files as these will be needed to identify pins.

## 1.1 Download and Install the Quartus Prime Lite Edition Software

The Quartus can run on Windows and different Linux distributions. The installation of the software has many steps. Please see the article <u>Intel® Quartus® Prime Lite and NIOS® II SBT for Eclipse Installation Instructions</u> on Annabooks.com to install the software needed for this hands-on exercise. All you need for this hands-on paper is the installation of the Quartus Prime Lite software with Max 10 support.

## 1.2 ADC Project

There are several parts in the MAX 10 family. The lower end of the family has 1 ADC block built in, and the upper end of the family has 2 ADC blocks.

The 10M08SAE144C8G that is on the evaluation kit board contains only 1 ADC block. To help create a design with the ADC, there is an ADC IP block that comes with the Quartus Prime software that can be used to create a design with the ADC. This IP block allows developers to quickly create a design without having to start from scratch. 10M08SAE144C8G's onboard 12-bit ADC has 8 input channels (CH1-CH8), a dedicated input channel 0 (ANIAN1), and a temperature sensing diode (TSD) channel as input. The 7 input channels are multiplexed with GPIOs. When the ADC is in the design, the ADC/GPIO multiplexed pins can only be used for ADC. A compilation error will occur if you try to make an assignment. The built-in temperature sensing diode (TSD) can measure the internal temperature of the MAX 10. The ADC is clocked using a phase-locked loop (PLL) The MAX 10 has 4 PLLs built in. IP blocks are used to implement the ADC and PLL into the design. For this hands-on example, we will create a design that uses two channels. The first is channel 1 which is

attached to a DC or AC source and the second is channel 7 which is connected to the R94  $10K\Omega$  trimmer pot. The ADC Toolkit that comes with Quartus Prime will read the output from the ADC.

#### 1.2.1 Create the Project

The first step is to create the design project.

- 1. Open Quartus.

- 2. Click on the New Project Wizard.

- 3. Click Next to the Introduction dialog.

- 4. Select or create a project directory c:\FPGA\ADC\_Example (Do not use the Quartus installation directory) and name the project "ADC0\_Example". Click Next.

**Note**: By default, the root directory is the Quartus installation directory. Make sure the root project directory is a separate path from the Quartus installation files.

- 5. Project Type: Empty project, click Next.

- 6. Add File, no files to add, click Next.

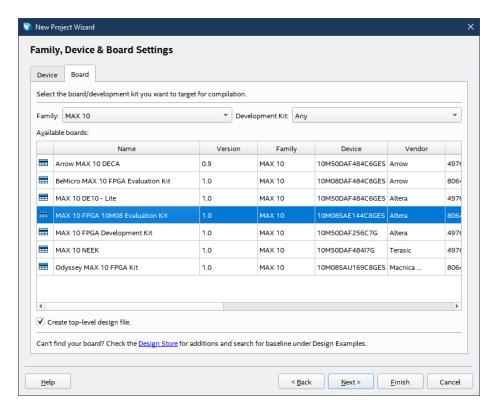

- 7. Family, Device & Board Settings, click the Board tab and select: MAX 10 FPGA 10M08 Evaluation Kit and click Next.

- 8. EDA Tools, click Next.

- Summary, click Finish.

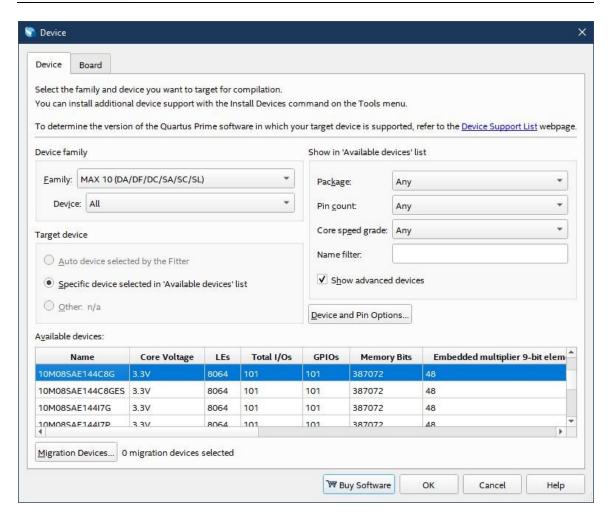

**Note**: The actual MAX 10 on our board is the 10M08SAE144C8G, thus it is not an Engineering Sample (ES). The next two steps change the device to the production device. Your experience might be different. These next two optional steps change the device.

- 10. In the project navigation pane on the left, right-click on 10: 10M08SAE144C8GE, and select Device from the context menu.

- 11. In the Available devices, scroll down and select the 10M08SAE144C8G, click OK.

#### 1.2.2 Create the Design Step 1: Platform Builder

Quartus supports many design types to create an FPGA design. The Platform Designer tool will be used for this hands-on exercise. Platform Builder makes it easy to add already-built IP blocks and interconnect them.

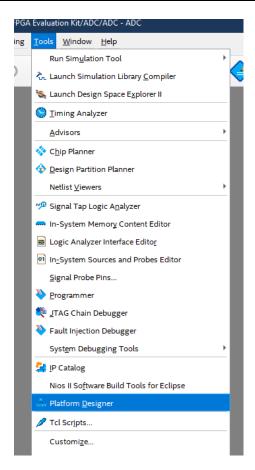

1. From the menu, select Tools->Platform Designer, or the Platform Designer icon from the toolbar.

The Platform Designer tool is launched. By default, a clock (clk\_0) is added to the design. Platform Designer tool makes it easy to add IP blocks and make interconnections between the blocks.

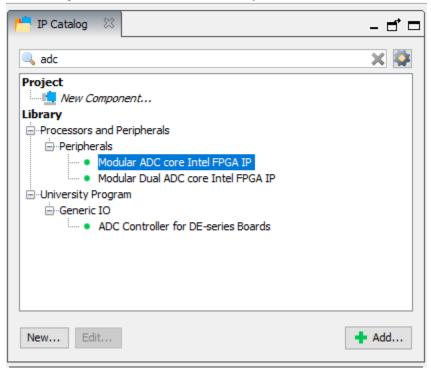

2. The top, left pane contains the IP Catalog with all the available IP blocks that come with Quartus Prime. In the search box, type ADC.

♣ Platform Designer - unsaved.qsys\* (E:\FPGA\Intel Max 10 FPGA Evaluation F

File Edit System Generate View Tools Help

3. Expanding the branches reveals the available IP. Double-click on Modular ADC core Intel FPGA IP. This will add the ADC IP to the design and open the Modular ADC core Intel FPGA IP configuration page.

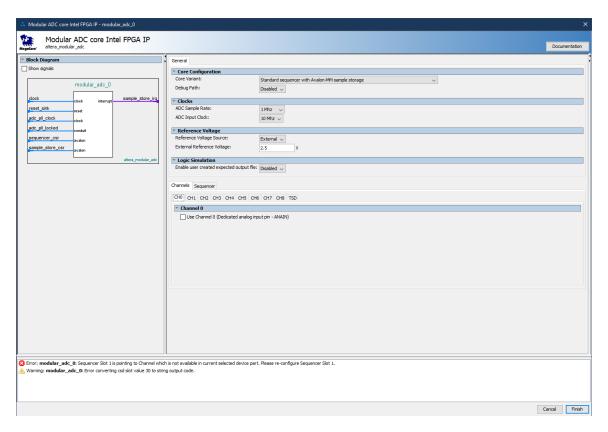

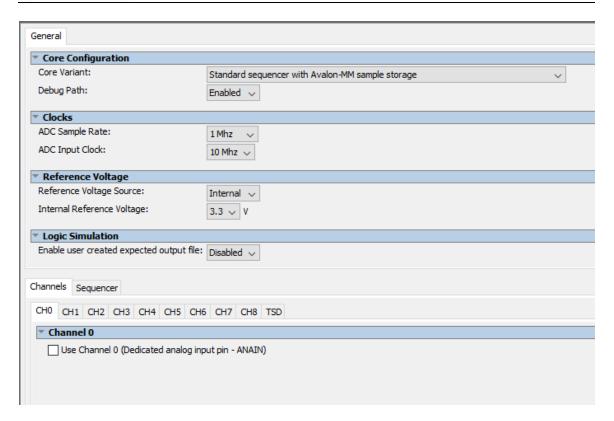

- 4. In the General tab, set the following:

- a. Core Variant: Standard sequencer with Avalon-MM sample storage.

- b. Debug Path: Enable.

- c. ADC Sample Rate: 1 MHz.

- d. ASC Input Clock: 10 MHz.

- e. Reference Voltage Source: External.

- f. Internal reference Voltage: 3.3V

- g. Enable user created expected output file: Disabled.

The ADC IP block supports several implementation variants. The one chosen will use the MAX 10's internal RAM to save the data. Since the ADC Toolkit will be used to monitor the ADC output, the Debug Path is set to Enabled. The evaluation kit has a 2.5 V reference voltage for the ADC; but since the 10K trimmer pot can supply 3.3 V to the channel, we will use the internal 3.3V.

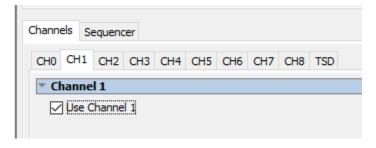

5. In the Channels tab, click on CH1, and check the "Use Channel 1" box.

- 6. Click on CH7, and check the "Use Channel 7" box.

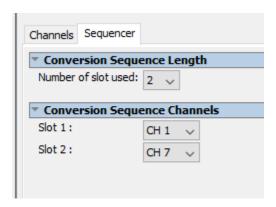

- 7. Click on the Sequencer tab.

- 8. Set the number of slots used to 3.

- 9. Set Slot 1: to CH1 and Slot 2: to CH 7.

- 10. Click Finish.

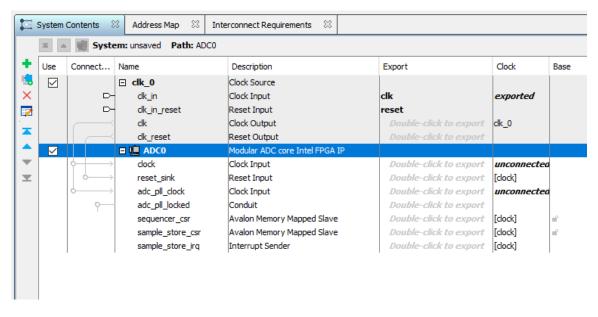

- 11. The ADC will be added to the design. In the System Contents, you will see the ADC has been added to the list of devices to be interconnected. Right-click on the name and rename the device to ADC0.

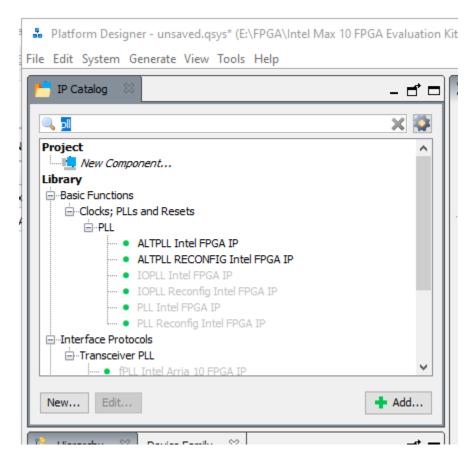

- 12. Now we need to add the PLL. In the IP Catalog, type pll in the search.

- 13. A number of different PLLs appear in the branches, but only a few are available. Double-click on the ALTPLL Intel FPGA IP to add to the design.

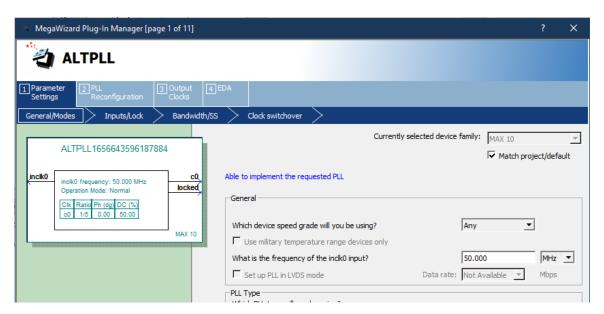

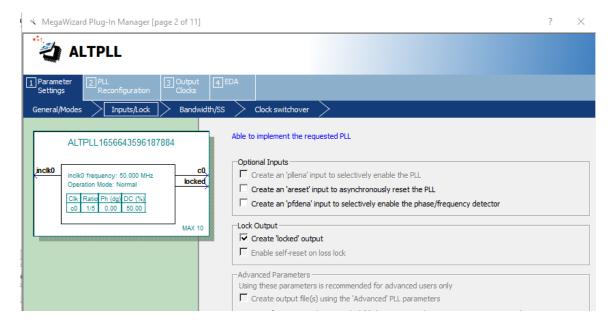

14. The PLL is added and the ALTPLL Intel FPGA IP configuration page appears. The configuration page has a workflow-like presentation. Tab 1 Parameter Settings contains the general settings for the PLL. For the "What is the frequency of the inclk0 input?" set the value to 50.000 MHz. The evaluation kit has a 50 MHz oscillator.

- 15. Click Next.

- 16. Optional: Uncheck the box next to "Create an 'areset' input to asynchronously reset the PLL". This signal is not needed for this design, and this will remove one warning from the list. Leave Create 'locked' output checked.

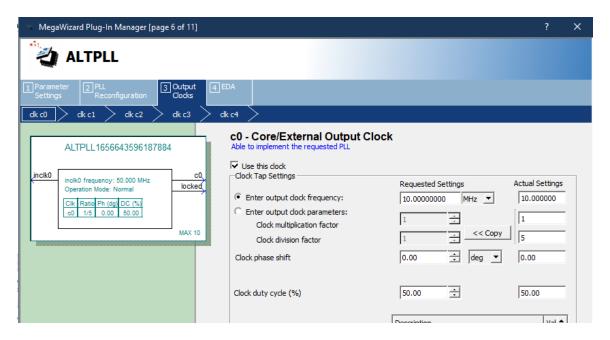

- 17. Click on 3. Output Clocks tab.

- 18. There are 5 output clock settings. All we need is clk c0. Under clk c0 click the radio button next to Enter output clock frequency.

- 19. Set the Requested Settings to 10.00 MHz. This is to match the input clock frequency of the ADC.

- 20. Click Finish.

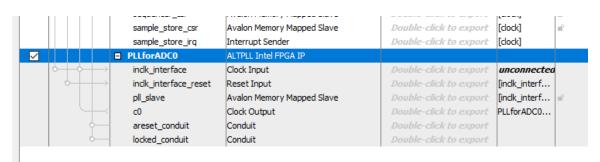

- 21. The PLL is added to the design. Rename the PLL to PLLforADC0. As there are 4 PLLs in the MAX 10, a good name helps show what the PLL is connected to.

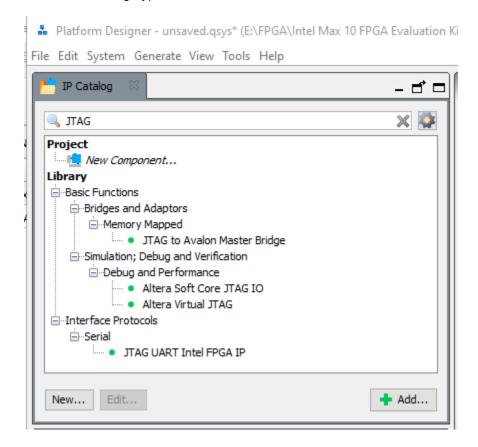

22. Last item to add is the JTAG bridge so we can interact with the ADC output using the ADC Tool. In the IP catalog, type JTAG in the search.

- 23. Double-click on the JTAG to Avalon Master Bridge to add it to the design.

- 24. A configuration page will appear. Click Finish.

- 25. Rename the JTAG to JTAGBridge.

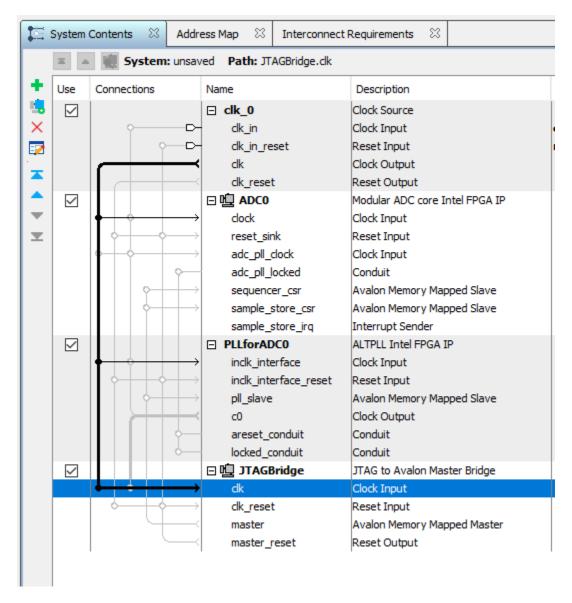

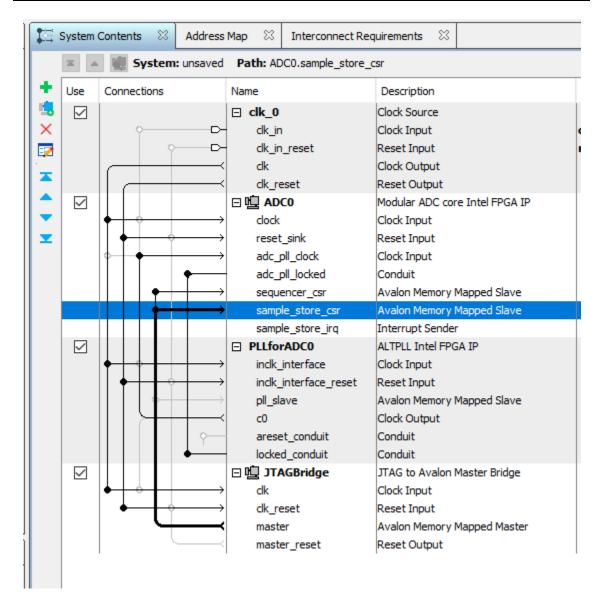

- 26. Now we need to connect everything together. The first step is to connect clk\_0 output to the 3 other devices. In the System Contents tab, click on the dots that connect clk\_0 Clock Output to the clock inputs for all three devices. Don't connect the adc\_pll\_clock to this line.

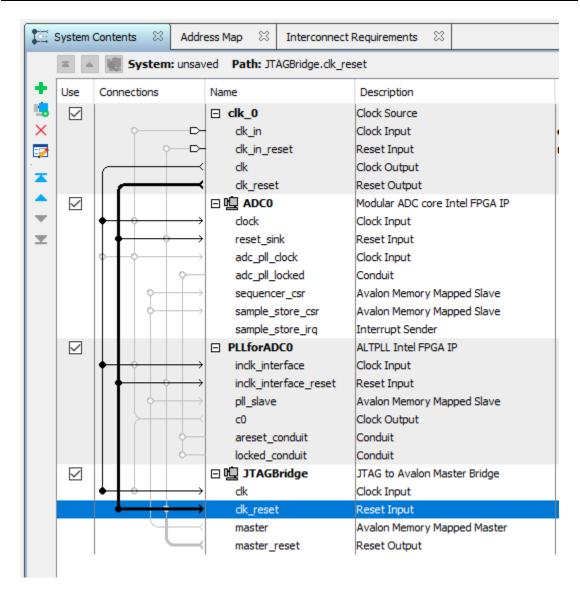

27. Now connect clk\_0's clk\_reset to the 3 devices' Reset Input pins.

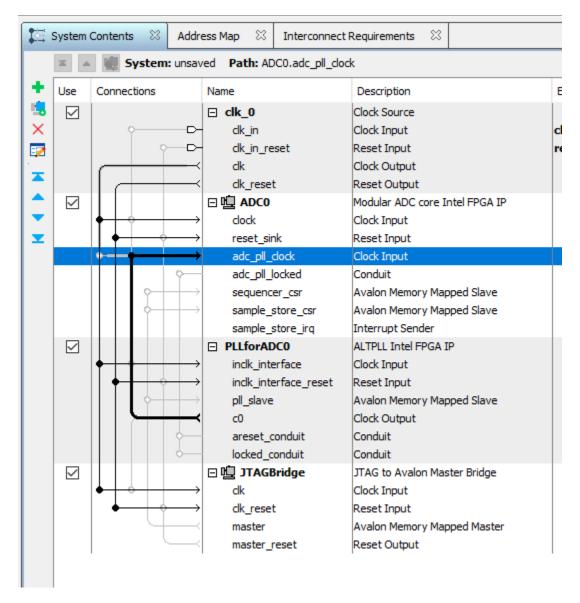

28. Next, we connect the PLL output clock (c0) to the ADC PLL clock input (adc\_pll\_clock).

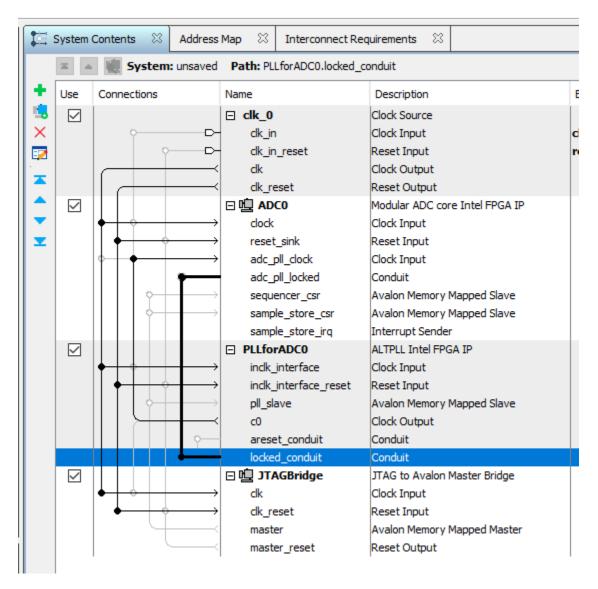

29. Connect the PLL's locked\_conduit to the ADC's asc\_pll\_locked pin.

30. We need the JTAG to be able to access the data. Connect the JTAGBridge's master to ADC0's sequence csr and sample store csr.

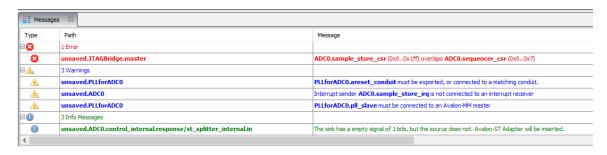

There will be an error after these connections are made since ADC lines have the same address.

31. To fix this error, change the sequencer\_ser base address to 200. Click on the base value of 0x000 0000 and change the value to 0x0000 0200. The error will go away.

- The design needs a base address to make the memory-mapped components unique. From the menu, select System->Assign Base Address.

- 33. We can now generate the HDL code. Click on the Generate HDL... button.

- 34. A Generation dialog appears. This will generate a block symbol file (.bsf) that we can use in the Block Diagram designer of Quartus. Keep the output Path the same as the project folder and click the Generate button.

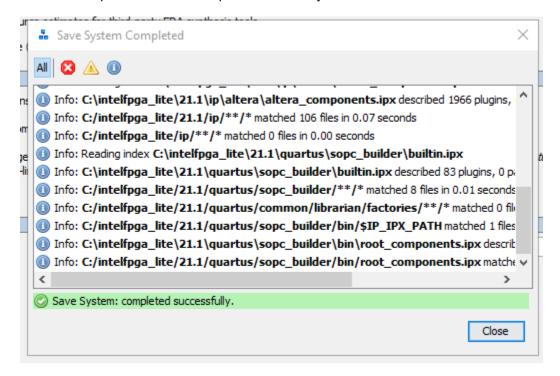

- 35. A dialog will appear asking to save the system. Click save.

- 36. Name the system ADC0 1MHz.gsys and click save.

- 37. The save process should complete successfully. Click close.

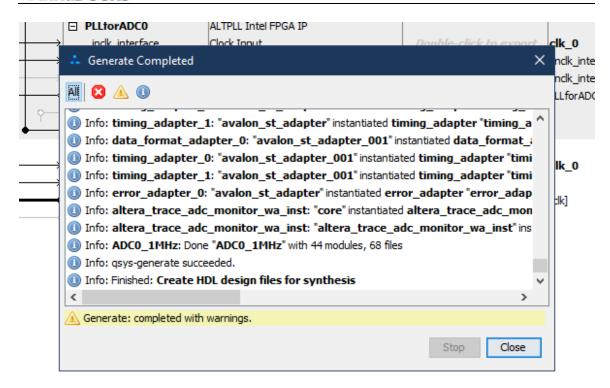

38. The Generate HDL process will run and should finish successfully. There will be warnings for items not connected, but for this exercise, they will not be needed. Click Close.

39. Click Finish to close the Platform Designer.

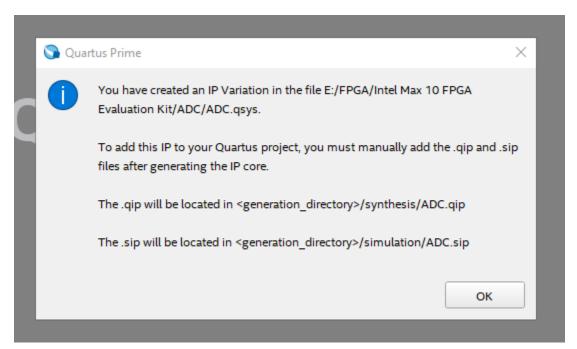

- 40. Once the ADC0\_1MHz design has been created, Quartus automatically reminds you to add the ADC0\_1MHz IP to the ADC design project. Click Ok.

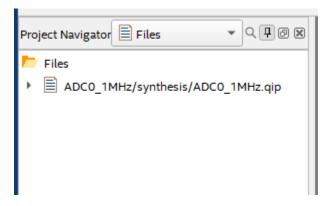

- 41. First, we need to add the newly create ADC block to the project. In the Project Navigator, click on the drop-down and select Files.

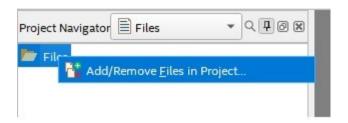

- 42. Right-Click on Files and select Add/Remote Files in Project.

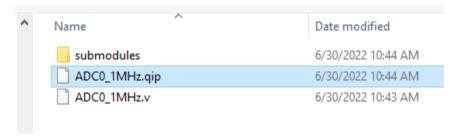

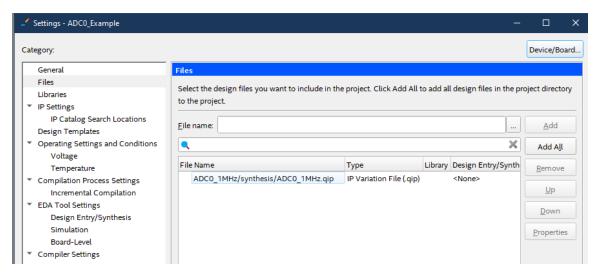

- 43. A Settings-ADC page appears with Files on the left highlighted. Click the three dots browse button for File name, and navigate to ADC\_Example\ADC0\_1MHz\synthesis folder.

- 44. Click on ADC0\_1Mhz.qip file and click open.

45. Click OK to close the Settings-ADC0\_Example page. The qip file is added to the Project navigator list. Underneath are all the Verilog files that were generated by Platform Builder.

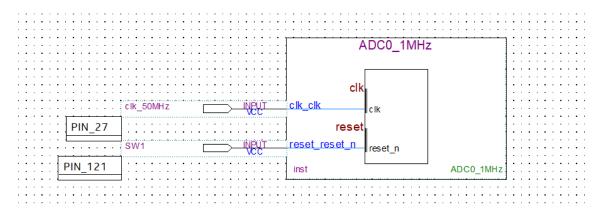

## 1.2.3 Create the Design Step 2: Block Diagram

With the ADC qip file added to the project, let's create the block diagram and complete the design.

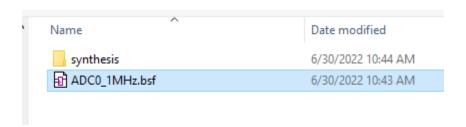

- 1. From the menu, select New->Block Diagram/Schematic File or the toolbar. Click Ok.

- The symbol window appears. Double-click on the symbol windows and the symbol dialog appears.

- 3. Click on the 3 dots to open the file browser.

- 4. Browse to \ADC Example\ADC0 1MHz folder and open the ADC0 1MHz.bsf file.

- 5. The symbol for the ADC0 1Mhz appears. Click OK to add the symbol to the schematic.

- 6. Drag the mouse with the ADC0\_1MHz symbol to a location on the diagram and then left-click to drop it in place.

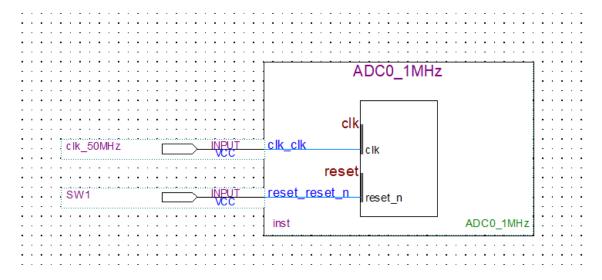

- 7. Right-click on the ADC0 1MHz symbol and select Generate Pins for Symbol Ports.

- 8. Change the name of the clk clk pin to clk 50MHz.

- Change the name of the reset\_reset\_n to SW1. The SW1 switch on the evaluation kit is connected to the FPGA DEV\_CLRN pin. The circuit for SW1 is logic 1 on startup and logic0 when pressed.

- 10. Save the schematic as ADC0 Example.bdf.

- 11. In the Task pane on the left, double-click on Fitter (Place & Route) to start the task. The analysis will take some time, and it should succeed in the end. This step helps to diagnose any errors and finds the Node Names for the pin assignments in the next step.

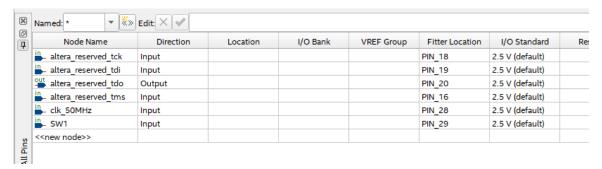

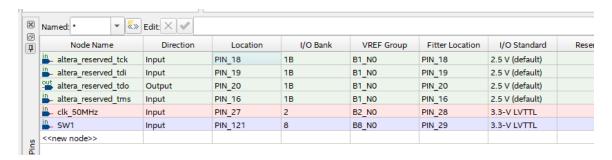

12. Once the process completes, the pin assignments need to be set. From the menu, select

Assignments->Pin Planner or click on the icon from the toolbar. The analysis that was just run populated the Node Name list at the bottom of the Pin Planner dialog.

13. Using the board schematic, locate the pins for the SW1 and the 50MHz clock. Set the Location values for both node names. For the MAX 10 – 10M08 Evaluation Board, these values are as follows:

| Node Name           | Location |

|---------------------|----------|

| SW1                 | PIN_121  |

| Clk_50MHz:          | PIN_27   |

| altera_reserved_tck | PIN_18   |

| altera_reserved_tdi | PIN_19   |

| altera_reserved_tdo | PIN_20   |

| altera_reserved_tms | PIN_16   |

14. Set the I/O Standard to 3.3V-LVTTL for both pins. You can see from the schematic that the I/O are all tied to 3.3V.

The ADC channel pins don't need to be assigned, since the ADC IP Block takes care of this already.

15. Close the Pin Planner when finished. The diagram gets updated with the pin numbers.

16. Save the project.

**Note**: A best practice at this point would be to make a backup of the project folder. Quartus can crash unexpectedly, since it appears to be written in Java.

17. Finally, compile the design. In the Task pane, right-click on Compile and Design and select

Start from the context menu, or you can click on the the project compiles successfully.

symbol in the toolbar. Make sure

| < <filter>&gt;</filter>           |                                             |

|-----------------------------------|---------------------------------------------|

| low Status                        | Successful - Thu Jun 30 11:11:41 2022       |

| uartus Prime Version              | 21.1.0 Build 842 10/21/2021 SJ Lite Edition |

| evision Name                      | ADC0_Example                                |

| op-level Entity Name              | ADC0_Example                                |

| amily                             | MAX 10                                      |

| evice                             | 10M08SAE144C8GES                            |

| iming Models                      | Preliminary                                 |

| otal logic elements               | 4,871 / 8,064 ( 60 % )                      |

| otal registers                    | 3271                                        |

| otal pins                         | 2 / 101 ( 2 % )                             |

| otal virtual pins                 | 0                                           |

| otal memory bits                  | 271,968 / 387,072 ( 70 % )                  |

| mbedded Multiplier 9-bit elements | 0 / 48 (0 %)                                |

| otal PLLs                         | 1 / 1 (100 %)                               |

| IFM blocks                        | 0/1(0%)                                     |

| DC blocks                         | 1/1(100%)                                   |

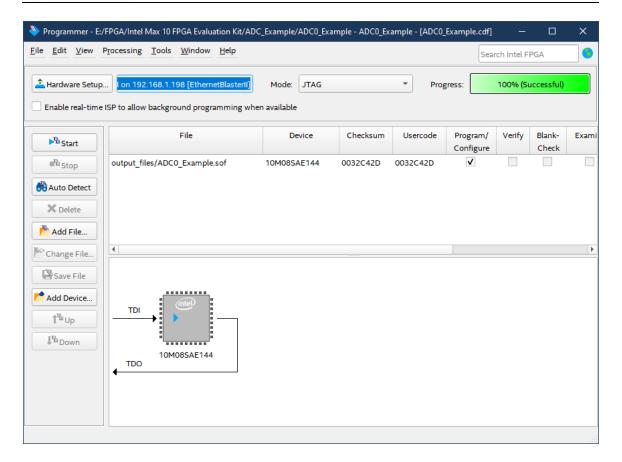

#### 1.2.4 Program the Board

With the design compiled, we can now test it on the board.

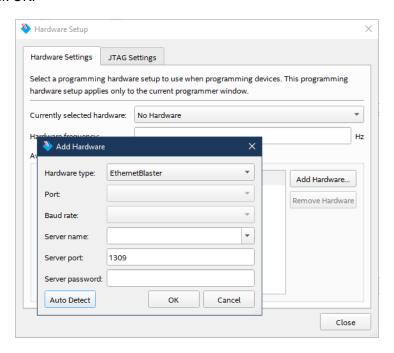

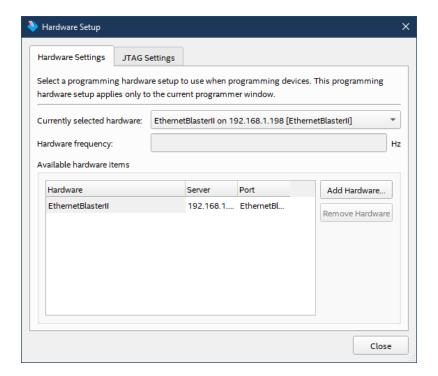

1. Connect the board and the programming cable together per the cable instructions.

**Note**: The MAX 10 – 10M08 Evaluation Kit doesn't come with a programming cable or built-in JTAG USB Blaster II. You will have to use either the USB Blaster II or EthernetBlaster II external cables. The EthernetBlaster II was used. DHCP setup was not working, so a direct Ethernet cable connection was made between a PC and the EthernetBlaster II. Set the static IP for the PC network card to 198.162.0.1. Access the EthernetBlaster II via a browser and then change the IP to a static IP that matches the network. The new IP address was used as the Server name. Your experience might be different.

- 2. Connect a signal generator to the board as follows:

- Signal out lead to J4-1 (Arduino connector Annalog\_IN0).

- Signal ground to J2-6 (Arduino connector GND).

- 3. Set the function generator to 1Khz 2VPP with a DC offset enabled and set for 1V positive.

- 4. Power on the board and the programming cable box.

- 5. In Quartus Prime, from the Task pane, right-click on Program Device (Open Programmer)

and select Open from the context menu or click on the icon on the toolbar.

- 6. When the Programmer dialog appears, click on the "Hardware Setup" button.

- 7. Click the Add hardware button, select the Hardware type, fill in any remaining information, and click OK.

8. The tool allows you to connect to a number of programming cables. We need to select the one for our board. In the "Currently selected hardware", click the drop-down, select the hardware cable for the board, and click Close when finished

9. An ADC0\_Example.sof file gets created during the Compile Design flow. The file is automatically filled in. There is only one FPGA on the board and in the JTAG chain, so the file already has the Program/Configure checkbox checked. Click the Start button to program the board. The process takes a few seconds and shows that the task completed successfully.

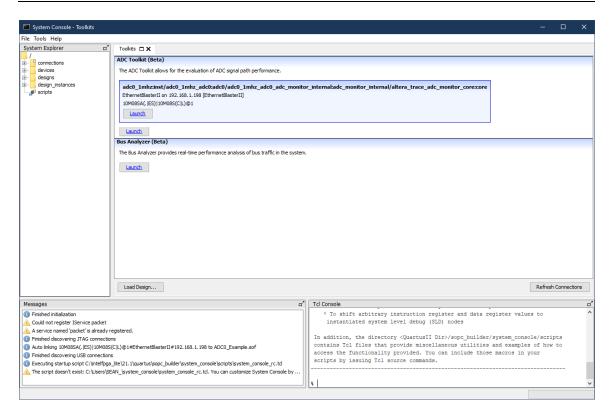

## 1.2.5 Test the Design with the ADC Toolkit

The board now has the system loaded in SRAM. The ADC Toolkit can view the output from the ADC.

- 1. Open Platform Builder

- 2. As Platform Builder launches, the pp[en file dialog opens asking to open the ADC0\_1MHz.qsys file. Open the ADC0\_1MHz.qsys file and the design will load.

- 3. From the menu, select Tools->System Console.

- 4. The console will read the JTAG and enable the ADC Toolkit. Click the Launch button to launch the ADC Toolkit.

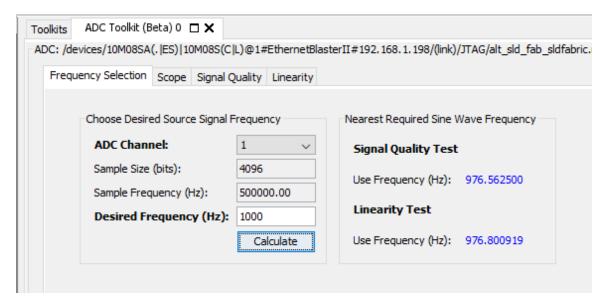

- 5. A new tab appears. Under Frequency Selection, click Calculate.

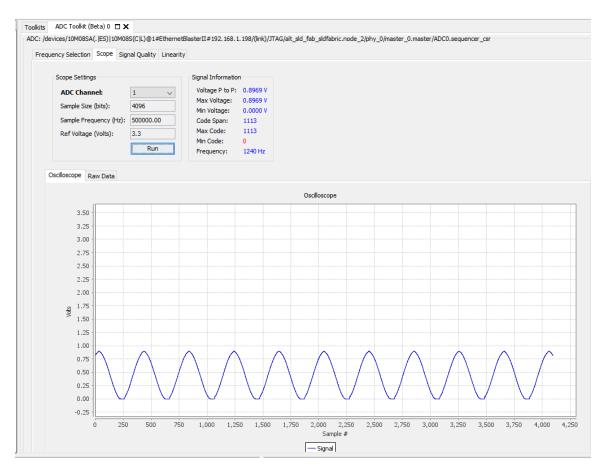

- Click on the Scope tab.

- 7. ADC\_Channel 1 should already be selected. The Scope tab looks like the screen of an Oscilloscope. Click the Run button, and you should see the sine wave appear.

- 8. Click on the Raw Data tab to see the actual values coming out of the ADC.

- 9. Click on Stop to stop gathering data.

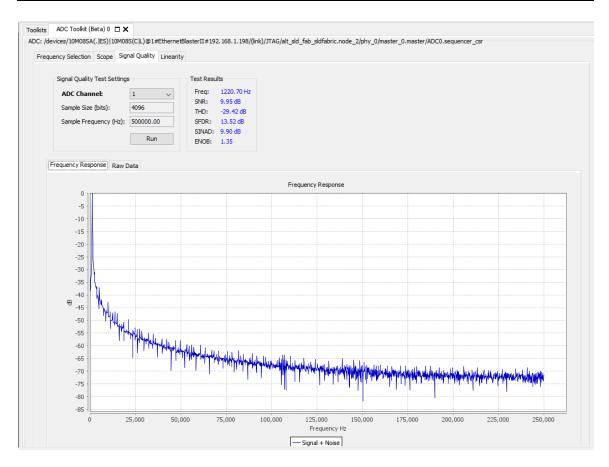

- 10. Click on the Signal Quality tab and then click the Run button. The command only runs for a few seconds and stops.

11. Click on the Raw Data tab to view the actual values.

The Linearity tab has several scope views: Histogram, DNL, INL, and Raw Data.

- 12. Go back to Scope, and change the ADC\_Channel to 7.

- 13. Click the Run button and adjust the  $10K\Omega$  trimmer pot in either direction to watch the voltage level change.

**Note**: TSD was left out of the original design, since there appears to be an issue enabling the TSD with the other two channels. This issue was not indicated in any of the documentation that we found. The old training examples stayed away from enabling the TSD. If you want to view the TSD, you can edit ADC0 in the Platform build. Deselect CH1 and CH7, and then enable TSD. Save and regenerate the system file, and click Finish to close Platform Builder. In Quartus, recompile the design and reprogram the board with the .sof file. Use the Raw Data in the ADC tool kit Scope tab to see the raw output files. Compare the HEX values to the table found in the Intel® MAX® 10 Analog to Digital Converter User Guide.

## 1.3 Summary: All the Little Steps

Platform Builder and the IP Blocks make it easy to create an FPGA design. The not-so-easy part was all of the little steps that are different from the older training material. Quartus even crashed in one iteration, and naming everything ADC in the first test crashed the compiler with name conflicts. Once the little issues and the TSD issue were resolved, designing and testing flows was very simple.

#### 1.4 References

The following references were used for this article:

- Intel® MAX® 10 Analog to Digital Converter User Guide -<a href="https://www.intel.com/content/www/us/en/docs/programmable/683596/20-1/analog-to-digital-converter-overview.html">https://www.intel.com/content/www/us/en/docs/programmable/683596/20-1/analog-to-digital-converter-overview.html</a>

- Introduction to Analog to Digital Conversion in Intel® MAX® 10 Devices Parts 1 and 2 -Intel FPGA training site Intel® FPGA Technical Training

- Using the ADC Toolkit in Intel® MAX® 10 Devices Intel FPGA training site <u>Intel® FPGA</u> <u>Technical Training</u>

- How to Create ADC Design in MAX 10 Device Using Qsys Tool - <u>https://cdrdv2.intel.com/v1/dl/getContent/649255?explicitVersion=true</u>

<u>https://www.youtube.com/watch?v=0oO1RFa-4Xk</u>

- Intel® MAX® 10-10M08 Evaluation Kit schematic file.

Altera 10M08S E144 eval schematic REV 1 0.pdf.