# A Simple Nios® II Implementation on Intel® MAX® 10-10M08 Evaluation Kit

By Sean D. Liming and John R. Malin Annabooks, LLC. – <u>www.annabooks.com</u>

November 2022

The Nios II is a 32-bit soft processor core for Intel FPGAs. The Nios II softcore processor is an IP block that comes with the Quartus Prime tools. The Nios II comes in two flavors Nios II/f (fast) and Nios II/e (economy). The Nios II/f is larger and takes up a few more Logical Elements in the chip, but it has MMU support for real-time operating system applications. Nios II/e is smaller with no MMU support. Nios II/f requires a license and the Nios II/e doesn't. In this hands-on exercise, we will create a simple Nios II/f design and run a hello world application on the new processor.

The Project Requirements:

- Intel Quartus Prime Lite Edition V21.0 and Nios® II SBT for Eclipse already installed.

- Intel® MAX® 10 10M08 Evaluation Kit and the schematic for the evaluation board are required. The schematic PDF file can be downloaded from the Intel FPGA website.

- Intel FPGA Programming cable USB Blaster II or EthernetBlaster II. The Intel® MAX® 10 10M08 Evaluation Kit doesn't have a built-in USB Blaster II on board.

- Intel® Quartus® Prime Lite and Nios® II SBT for Eclipse Installation Instructions on Annabooks.com

**Note**: There are equivalent MAX 10 development and evaluation boards available. These boards can also be used as the target, but you will have to adjust to the available features on the board. Please make sure that you have the board's schematic files as these will be needed to identify pins.

Windows was used as the host OS during the development of this paper, and there were problems running the development tools on Windows. Eclipse is the application development environment, which by itself is not a problem. The issue is that Linux commands are required to set up and build application projects. The Windows Subsystem for Linux has to be installed along with a Linux distribution such as Ubuntu. There were many little steps to getting all these items set up. Even after all the little steps to get Eclipse running were taken, applications would fail to build because "make" was not found. After a few searches and comparison tests with an Ubuntu setup were made, all the little steps necessary to get the software to build and run were worked out. Please see the article <u>Intel® Quartus® Prime Lite and Nios® II SBT for Eclipse Installation Instructions</u> on Annabooks.com to install the software needed for this hands-on exercise.

### 1.1 Basic Nios II Project

For this design, we will have a Nios II processor IP block, along with an onboard RAM IP Block, and a JTAG UART IP Block. The application will simply send messages out the JTAG interface to a console application running in Eclipse. There are two parts to the design process. The first involves creating the hardware design in Quartus Prime and Platform Builder. The second step is to create the application with Eclipse.

### 1.1.1 Create the Project

The first step is to create a design project.

- 1. Open Quartus.

- 2. Click on the New Project Wizard.

- 3. Click Next to the Introduction dialog.

- 4. Select or create a project directory \NIOSii\_Example (Do not use the Quartus installation directory) and name the project: "NIOS2CPU". Click Next.

**Note**: By default, the root directory is the Quartus installation directory. Make sure the root project directory is a separate path from the Quartus installation files. Also, there can be no spaces in the name of the folders or projects.

- 5. Project Type: Empty project, click Next.

- 6. Add File: no files to add, click Next.

- 7. Family, Device & Board Settings: click the Board tab and select: MAX 10 FPGA 10M08 Evaluation Kit. Click Next.

| Devic<br>Selec  | t the board/development kit you want to target                                        | for compila | ation. |              |         |                  |         |      |

|-----------------|---------------------------------------------------------------------------------------|-------------|--------|--------------|---------|------------------|---------|------|

| ami             | ly: MAX 10                                                                            | -           | Develo | pment Kit:   | Any     |                  |         | *    |

| A <u>v</u> aili | able boards:                                                                          |             |        |              |         |                  |         |      |

|                 | Name                                                                                  | Vers        | ion    | Fami         | ly      | Device           | Vendor  |      |

|                 | Arrow MAX 10 DECA                                                                     | 0.9         |        | MAX 10       |         | 10M50DAF484C6GES | Arrow   | 4976 |

|                 | BeMicro MAX 10 FPGA Evaluation Kit                                                    | 1.0         |        | MAX 10       |         | 10M08DAF484C8GES | Arrow   | 8064 |

|                 | MAX 10 DE10 - Lite                                                                    | 1.0         |        | MAX 10       |         | 10M50DAF484C6GES | Altera  | 4976 |

|                 | MAX 10 FPGA 10M08 Evaluation Kit                                                      | 1.0         |        | MAX 10       |         | 10M08SAE144C8GES | Altera  | 8064 |

|                 | MAX 10 FPGA Development Kit                                                           | 1.0         |        | MAX 10       |         | 10M50DAF256C7G   | Altera  | 4976 |

|                 | MAX 10 NEEK                                                                           | 1.0         |        | MAX 10       |         | 10M50DAF484I7G   | Terasic | 4976 |

|                 | Odyssey MAX 10 FPGA Kit                                                               | 1.0         |        | MAX 10       |         | 10M08SAU169C8GES | Macnica | 8064 |

|                 | reate top-level design file.<br>find your board? Check the <u>Design Store</u> for ad | ditions and | search | for baseline | under I | Design Examples. |         | •    |

- 8. EDA Tools: click Next.

- 9. Summary: click Finish

**Note**: The actual MAX 10 on our board is the 10M08SAE144C8G, thus it is not an Engineering Sample (ES). The next two steps change the device to the production device. Your experience might be different. These next two optional steps change the device.

- 10. In the project navigation pane on the left, right-click on 10: 10M08SAE144C8GE, and select Device from the context menu.

- 11. In the Available devices, scroll down and select the 10M08SAE144C8G. Click OK.

| Device Bo        | ard                                                                                                                                |                                                                  |             |                       |                   |              |              |                                              |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------|-----------------------|-------------------|--------------|--------------|----------------------------------------------|--|--|--|

| You can instal   | l addition:                                                                                                                        | vice you want to ta<br>al device support v<br>n of the Quartus P | vith the In | istall Devices co     |                   |              |              | efer to the <u>Device Support List</u> webpa |  |  |  |

| Device family    |                                                                                                                                    |                                                                  |             |                       | Show in 'A        | vailable de  | vices' li    | st                                           |  |  |  |

| Eamily: M        | amily: MAX 10 (DA/DF/DC/SA/SC/SL)                                                                                                  |                                                                  |             |                       |                   | age: Any     |              | ÷                                            |  |  |  |

| Dev <u>i</u> ce: | Device: All                                                                                                                        |                                                                  |             |                       |                   |              | Any          |                                              |  |  |  |

| Target device    |                                                                                                                                    |                                                                  | Core sp     | Core speed grade: Any |                   | •            |              |                                              |  |  |  |

| -                | <ul> <li><u>A</u>uto device selected by the Fitter</li> <li><u>S</u>pecific device selected in 'Available devices' list</li> </ul> |                                                                  |             |                       |                   |              | Name filter: |                                              |  |  |  |

| Available devid  |                                                                                                                                    |                                                                  |             |                       | <u>D</u> evice ar | nd Pin Optic | ons          |                                              |  |  |  |

| Name             |                                                                                                                                    | Core Voltage                                                     | LEs         | Total I/Os            | GPIOs             | Memor        | y Bits       | Embedded multiplier 9-bit elem               |  |  |  |

| 10M08SAE14       | 44C8G                                                                                                                              | 3.3V                                                             | 8064        | 101                   | 101               | 387072       |              | 48                                           |  |  |  |

| 10M08SAE14       | 44C8GES                                                                                                                            | 3.3V                                                             | 8064        | 101                   | 101               | 387072       |              | 48                                           |  |  |  |

| 10M08SAE14       | 1417G                                                                                                                              | 3.3V                                                             | 8064        | 101                   | 101               | 387072       |              | 48                                           |  |  |  |

|                  | 14I7P                                                                                                                              | 3 3V                                                             | 8064        | 101                   | 101               | 387072       |              | 48                                           |  |  |  |

| 10M0854F14       |                                                                                                                                    |                                                                  |             |                       |                   |              |              |                                              |  |  |  |

### 1.1.2 Create the Design Step 1: Platform Designer

Quartus supports many design types to create an FPGA design. The Platform Designer tool will be used for this hands-on exercise. Platform Builder makes it easy to add already-built IP blocks and interconnect them.

1. From the menu, select Tools->Platform Designer, or the Platform Designer icon from the toolbar.

The Platform Designer tool is launched. By default, a clock (clk\_0) is added to the design. Platform Designer makes it easy to add IP blocks and make interconnections between the blocks.

2. The top left pane contains the IP Catalog with all the available IP blocks that come with Quartus Prime. In the search box, type NIOS.

| 📩 IP Catalog 🛛 | - <b>-</b>                                                                                                                                                                                                                                                                                                                                                             |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 🔍 NIOS         | × 🕸                                                                                                                                                                                                                                                                                                                                                                    |

|                | ebug and Verification<br>n<br>lios II Custom Instruction Master BFM Intel FPGA IF<br>lios II Custom Instruction Slave BFM Intel FPGA IP<br>eripherals<br>'s<br>ustom Instructions<br>litswap<br>Custom Instruction Interconnect<br>Custom Instruction Master Translator<br>Custom Instruction Slave Translator<br>Eloating Point Hardware<br>floating Point Hardware 2 |

| <              | >                                                                                                                                                                                                                                                                                                                                                                      |

| New Edit       | 🛨 Add                                                                                                                                                                                                                                                                                                                                                                  |

- 3. Expand the Processors and Peripherals and the Embedded Processors branches. Under Embedded Processors double-click on the Nios II Processor.

- 4. This will open the Nios II Configuration page. The first tab is used to select the type of core Nios II/e or Nios II/f. We will keep the Nios II/f default for this exercise. Click Finish.

| Nios Il Processor - nios2_gen2_0                                                                                                                                                 |                      |                                                |                                                                                | ×                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------|

| Nios II Processor                                                                                                                                                                |                      |                                                |                                                                                | ·                                     |

| MegaCore altera_1052_genz                                                                                                                                                        |                      |                                                |                                                                                | Documentation                         |

| * Block Diagram                                                                                                                                                                  | Main Vectors         | Caches and Memory Interfaces Arithmetic Instru | ctions MMU and MPU Settings JTAG Debug Adv                                     | vanced Features                       |

| Show signals                                                                                                                                                                     | T Select an I        | nplementation                                  |                                                                                |                                       |

| nios2_gen2_0                                                                                                                                                                     | Nios II Core:        | ○ Nios II/e                                    |                                                                                |                                       |

| cik ckck avaion data_master_                                                                                                                                                     |                      | Nios II/f                                      |                                                                                |                                       |

| reset avaion instruction_master                                                                                                                                                  |                      | Nios II/e                                      | Nios II/f                                                                      |                                       |

| irg interrupt reset debug_reset_request                                                                                                                                          | Summary              | Resource-optimized 32-bit RISC                 | Performance-optimized 32-bit RISC                                              |                                       |

| debug_mem_slave avalon nios_oustorm_instruction custorm_instruction_master                                                                                                       | Features             | JTAG Debug                                     | JTAG Debug                                                                     |                                       |

| atera_niss2_gen2                                                                                                                                                                 |                      | ECC RAM Protection                             | Hardware Multiply/Divide<br>Instruction/Data Caches<br>Tightly-Coupled Masters |                                       |

|                                                                                                                                                                                  |                      |                                                | ECC RAM Protection                                                             |                                       |

|                                                                                                                                                                                  |                      |                                                | External Interrupt Controller<br>Shadow Register Sets                          |                                       |

|                                                                                                                                                                                  |                      |                                                | MPU<br>MMU                                                                     |                                       |

|                                                                                                                                                                                  | RAM Usage            | 2 + Options                                    | 2 + Options                                                                    |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                | · · · · · · · · · · · · · · · · · · · |

| Error: nios2_gen2_0: Instruction Cache is larger than the Instruction Address. Please reduce<br>Error: nios2_gen2_0: Reset slave is not specified. Please select the reset slave | the Instruction Cach | e Size. Current Tag Size is 0                  |                                                                                |                                       |

| Error: nios2_gen2_0: Exception slave is not specified. Please select the exception slave                                                                                         |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

|                                                                                                                                                                                  |                      |                                                |                                                                                | Cancel Finish                         |

|                                                                                                                                                                                  |                      |                                                |                                                                                |                                       |

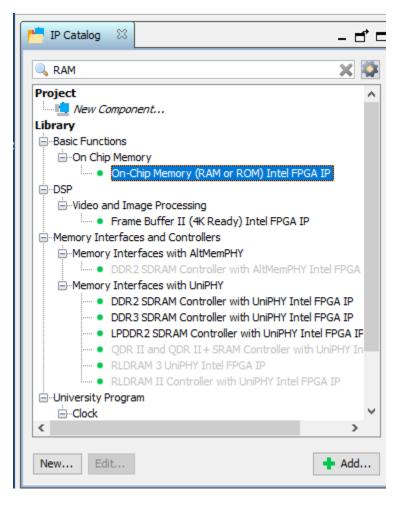

- 5. Now let's add the RAM IP block. In the IP Catalog enter RAM in the search box.

- 6. Double-click on On-chip Memory (RAM or ROM) in the Intel FPGA IP.

7. The configuration page will appear. Change the Total memory size to 8192 and click Finish.

| ▼ Size                                        |       |       |  |  |  |  |  |

|-----------------------------------------------|-------|-------|--|--|--|--|--|

| Enable different width for Dual-port a        | ccess |       |  |  |  |  |  |

| Slave S1 Data width:                          | 32 🗸  |       |  |  |  |  |  |

| Total memory size:                            | 8192  | bytes |  |  |  |  |  |

| Minimize memory block usage (may impact fmax) |       |       |  |  |  |  |  |

|                                               |       |       |  |  |  |  |  |

| Read latency                                  |       |       |  |  |  |  |  |

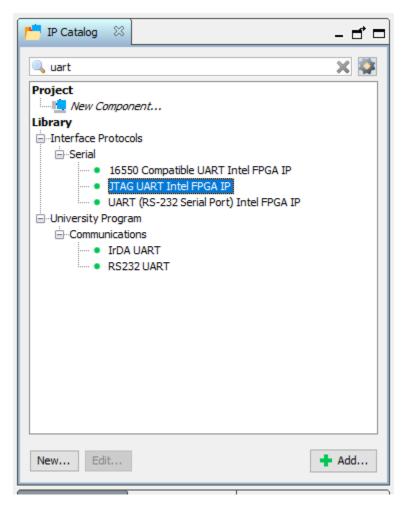

- 8. In the IP Catalog search, enter uart.

- 9. Double-click on the JTAG UART Intel FPGA IP.

- 10. A configuration page will appear. There are no changes to be made. Click Finish.

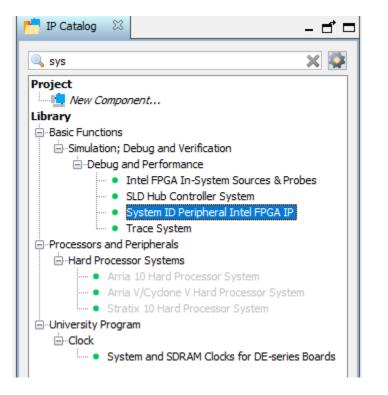

- 11. In the IP Catalog search, enter the system ID.

- 12. Double-click on the System ID Peripheral Intel FPGA IP.

13. A configuration page will appear. There are no changes to be made. Click Finish.14. Rename the IP blocks as follows:

- nios2\_gen2\_cpu

- onchip\_RAM

- jtag\_uart

- sysid

|    | <b>A</b>     | System: unsave           | d Path: nios2_gen2_cpu         |                                    |           |

|----|--------------|--------------------------|--------------------------------|------------------------------------|-----------|

| ۰. | Use          | Connections              | Name                           | Description                        | Export    |

| ٩, |              |                          | ⊡ clk_0                        | Clock Source                       |           |

| ×  |              | C                        | ⊢ dk_in                        | Clock Input                        | clk       |

| 2  |              | <u>ү</u> —с              | ← dk_in_reset                  | Reset Input                        | reset     |

|    |              |                          | < dk                           | Clock Output                       | Double-cl |

| •  |              |                          | <pre> dk_reset</pre>           | Reset Output                       | Double-cl |

|    |              |                          | 🗉 🛄 nios2_gen2_cpu             | Nios II Processor                  |           |

| •  |              | ¢                        | → dk                           | Clock Input                        | Double-c  |

|    |              | ¢                        | > reset                        | Reset Input                        | Double-c  |

|    |              |                          | < data_master                  | Avalon Memory Mapped Master        | Double-c  |

|    |              |                          | instruction_master             | Avalon Memory Mapped Master        | Double-c  |

|    |              |                          | → irq                          | Interrupt Receiver                 | Double-c  |

|    |              | $         \vdash \vdash$ | <pre>debug_reset_request</pre> | Reset Output                       | Double-c  |

|    |              |                          | debug_mem_slave                | Avalon Memory Mapped Slave         | Double-c  |

|    |              | ×—                       | custom_instruction_m           | . Custom Instruction Master        | Double-c  |

|    |              |                          | onchip_RAM                     | On-Chip Memory (RAM or ROM) Intel  |           |

|    |              | ♦                        | > dk1                          | Clock Input                        | Double-cl |

|    |              |                          | ⇒ s1                           | Avalon Memory Mapped Slave         | Double-c  |

|    |              |                          | > reset1                       | Reset Input                        | Double-c  |

|    | $\checkmark$ |                          | 🗆 jtag_uart                    | JTAG UART Intel FPGA IP            |           |

|    |              |                          | → dk                           | Clock Input                        | Double-c  |

|    |              |                          | > reset                        | Reset Input                        | Double-c  |

|    |              |                          | avalon_jtag_slave              | Avalon Memory Mapped Slave         | Double-c  |

|    |              | ↓ ↓                      | < irq                          | Interrupt Sender                   | Double-c  |

|    |              |                          | 🗆 sysid                        | System ID Peripheral Intel FPGA IP |           |

|    |              | ¢                        | → dk                           | Clock Input                        | Double-cl |

|    |              | ♦ ♦                      | reset                          | Reset Input                        | Double-cl |

|    |              | <u> </u>                 | control_slave                  | Avalon Memory Mapped Slave         | Double-cl |

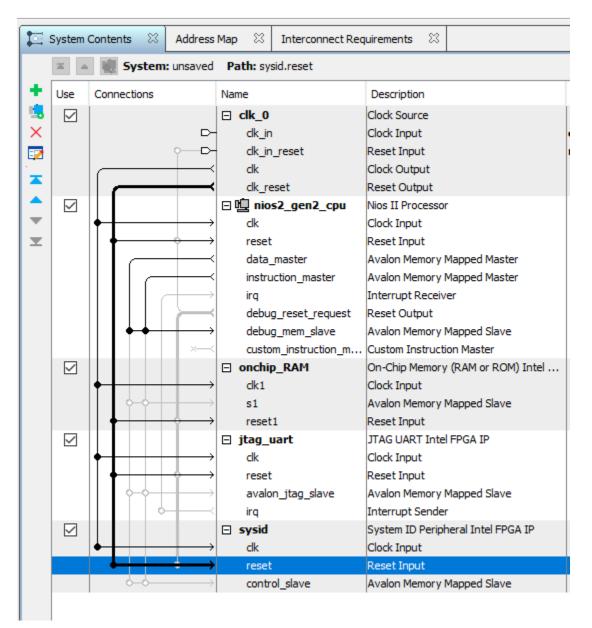

15. Now we need to wire the IP blocks together. First, wire all the clk lines together by clicking on the dots for all four IP blocks.

| +        | Use          | Connections | Name                   | Description                        |

|----------|--------------|-------------|------------------------|------------------------------------|

| 1.       |              |             | ⊟ clk_0                | Clock Source                       |

| ×        |              |             | - dk_in                | Clock Input                        |

| 7        |              | °— <b>□</b> | dk_in_reset            | Reset Input                        |

| .        |              |             | <b>k</b> dk            | Clock Output                       |

| -        |              |             | dk_reset               | Reset Output                       |

|          | $\checkmark$ |             | 回咀 nios2_gen2_cpu      | Nios II Processor                  |

| •        |              | •           | → clk                  | Clock Input                        |

| <b>x</b> |              | ¢           | reset                  | Reset Input                        |

|          |              |             | <pre>data_master</pre> | Avalon Memory Mapped Master        |

|          |              |             | instruction_master     | Avalon Memory Mapped Master        |

|          |              |             | irq                    | Interrupt Receiver                 |

|          |              |             | debug_reset_request    | Reset Output                       |

|          |              |             | debug_mem_slave        | Avalon Memory Mapped Slave         |

|          |              | ×           | custom_instruction_m   |                                    |

|          |              |             | onchip_RAM             | On-Chip Memory (RAM or ROM) Intel  |

|          |              | <b>†</b>    | dk1                    | Clock Input                        |

|          |              |             | s1                     | Avalon Memory Mapped Slave         |

|          |              |             | reset1                 | Reset Input                        |

|          |              |             | ⊡ jtag_uart            | JTAG UART Intel FPGA IP            |

|          |              | 1           | → dk                   | Clock Input                        |

|          |              |             | reset                  | Reset Input                        |

|          |              |             | avalon_jtag_slave      | Avalon Memory Mapped Slave         |

|          |              | ○           | irq                    | Interrupt Sender                   |

|          |              |             | ⊡ sysid                | System ID Peripheral Intel FPGA IP |

|          |              |             | ck<br>reset            | Clock Input<br>Reset Input         |

|          |              |             | control_slave          | Avalon Memory Mapped Slave         |

16. Next, connect all the reset lines together by clicking on the dots for all four IP blocks.

- 17. The memory lines have to be connected together. The s1 line in the RAM and Avalon\_jtag\_slave line in jtag\_uart will be connected to the nios2\_gen\_cpu data\_master and instruction master lines. Click on the dots for each IP block.

- 18. Connect the sysid control\_slave to nios2\_gen\_cpu data\_master.

Rev 1.4

|              | Contents 🛛       | Address Map                   |                          | quirements 🛛                       |

|--------------|------------------|-------------------------------|--------------------------|------------------------------------|

|              | System:          | unsaved Pa                    | ath: sysid.control_slave | 1                                  |

| Use          | Connections      | Nar                           | ne                       | Description                        |

|              |                  |                               | clk_0                    | Clock Source                       |

|              |                  |                               | clk_in                   | Clock Input                        |

|              |                  |                               | dk_in_reset              | Reset Input                        |

|              |                  | <                             | clk                      | Clock Output                       |

|              |                  | <                             | dk_reset                 | Reset Output                       |

| $\checkmark$ |                  |                               | 🗓 nios2_gen2_cpu         | Nios II Processor                  |

|              | ♦                | $\rightarrow$                 | clk                      | Clock Input                        |

|              | +                | $\leftrightarrow \rightarrow$ | reset                    | Reset Input                        |

|              |                  | <b>—</b>                      | data_master              | Avalon Memory Mapped Master        |

|              |                  | <b></b>                       | instruction_master       | Avalon Memory Mapped Master        |

|              |                  | $\rightarrow$                 | irq                      | Interrupt Receiver                 |

|              |                  | $\geq$                        | debug_reset_request      | Reset Output                       |

|              | 🛉 🖶              | $\rightarrow$                 | debug_mem_slave          | Avalon Memory Mapped Slave         |

|              |                  | ×                             | custom_instruction_m     | Custom Instruction Master          |

|              |                  | Ξ                             | onchip_RAM               | On-Chip Memory (RAM or ROM) Inte   |

|              | <b>+        </b> | $\rightarrow$                 | dk1                      | Clock Input                        |

|              | 🛉 🖶              | $\rightarrow$                 | s1                       | Avalon Memory Mapped Slave         |

|              | ││ <b>┿┨┨</b> ── | $\rightarrow$                 | reset1                   | Reset Input                        |

| $\checkmark$ |                  |                               | jtag_uart                | JTAG UART Intel FPGA IP            |

|              | <b>+        </b> | $\rightarrow$                 | clk                      | Clock Input                        |

|              | +                | $\leftrightarrow \rightarrow$ | reset                    | Reset Input                        |

|              | 🛉 🛉 🕂            | $\rightarrow$                 | avalon_jtag_slave        | Avalon Memory Mapped Slave         |

|              |                  |                               | irq                      | Interrupt Sender                   |

|              |                  |                               | sysid                    | System ID Peripheral Intel FPGA IP |

|              | •                | $\rightarrow$                 | clk                      | Clock Input                        |

|              | •                | $\rightarrow$                 | reset                    | Reset Input                        |

|              | - +              | $\longrightarrow$             | control_slave            | Avalon Memory Mapped Slave         |

19. Finally, connect the jtaq\_uart irq line to the nios2\_gen2\_cpu.

| фя s | System (     | Contents 🛛       | Address                       | Map 🛛 Interconnect Req | uirements 🖾                        | _ |

|------|--------------|------------------|-------------------------------|------------------------|------------------------------------|---|

|      | *            | 😻 System:        | unsaved                       | Path: jtag_uart.irq    |                                    |   |

| •    | Use          | Connections      |                               | Name                   | Description                        |   |

|      |              |                  |                               | ⊡ clk_0                | Clock Source                       | Ì |

| ×    |              |                  | ⊳                             | dk_in                  | Clock Input                        |   |

| 2    |              |                  | $\sim - \mathbf{P}$           | dk_in_reset            | Reset Input                        |   |

|      |              |                  |                               | dk                     | Clock Output                       |   |

| ▲    |              |                  |                               | dk_reset               | Reset Output                       |   |

| ▲    |              |                  |                               | 回 喧 nios2_gen2_cpu     | Nios II Processor                  | I |

| •    |              | •                | $\rightarrow$                 | dk                     | Clock Input                        |   |

| z    |              | ↓                | $\rightarrow \rightarrow$     | reset                  | Reset Input                        |   |

|      |              |                  |                               | data_master            | Avalon Memory Mapped Master        |   |

|      |              |                  |                               | instruction_master     | Avalon Memory Mapped Master        |   |

|      |              |                  | <b>→</b>                      | irq                    | Interrupt Receiver                 |   |

|      |              |                  | $\succ$                       | debug_reset_request    | Reset Output                       |   |

|      |              | │ │ <b>┿ ┿ ╂</b> | $\rightarrow$                 | debug_mem_slave        | Avalon Memory Mapped Slave         |   |

|      |              |                  | ×                             | custom_instruction_m   | Custom Instruction Master          |   |

|      |              |                  |                               | onchip_RAM             | On-Chip Memory (RAM or ROM) Intel  |   |

|      |              | <b>♦        </b> | $\rightarrow$                 | dk1                    | Clock Input                        |   |

|      |              | │                | $\rightarrow$                 | s1                     | Avalon Memory Mapped Slave         |   |

|      |              | │                | $\rightarrow \rightarrow$     | reset1                 | Reset Input                        |   |

|      | $\checkmark$ |                  |                               | 🗆 jtag_uart            | JTAG UART Intel FPGA IP            |   |

|      |              | <b>♦        </b> | $\rightarrow$                 | clk                    | Clock Input                        |   |

|      |              | │                | $\leftrightarrow \rightarrow$ | reset                  | Reset Input                        |   |

|      |              | │ │ <b>┿ ┿ ╂</b> | $\rightarrow$                 | avalon_jtag_slave      | Avalon Memory Mapped Slave         |   |

|      |              |                  | +                             | irq                    | Interrupt Sender                   |   |

|      |              |                  |                               | 🗆 sysid                | System ID Peripheral Intel FPGA IP |   |

|      |              | •                | $\rightarrow$                 | clk                    | Clock Input                        | 1 |

|      |              | •                | $\rightarrow \rightarrow$     | reset                  | Reset Input                        |   |

|      |              | <b>• •</b>       | $\longrightarrow$             | control_slave          | Avalon Memory Mapped Slave         | 1 |

20. If you scroll to the right, the irq is given a default value.

| <br>  |               |                      |                                    |                        |        |    |         |        |       |  |

|-------|---------------|----------------------|------------------------------------|------------------------|--------|----|---------|--------|-------|--|

|       |               | instruction_master   | Avalon Memory Mapped Master        | Double-click to export | [clk]  |    |         |        |       |  |

|       | $\rightarrow$ | irq                  | Interrupt Receiver                 | Double-click to export | [clk]  |    | IRQ 0   | IRQ :  | 31    |  |

|       |               | debug_reset_request  | Reset Output                       | Double-click to export | [clk]  |    |         |        |       |  |

| ++    | $\rightarrow$ | debug_mem_slave      | Avalon Memory Mapped Slave         | Double-click to export | [clk]  | ÷. | 0x0800  | 0x0fff |       |  |

|       | ×             | custom_instruction_m | Custom Instruction Master          | Double-click to export |        |    |         |        |       |  |

|       |               | onchip_RAM           | On-Chip Memory (RAM or ROM) Intel  |                        |        |    |         |        |       |  |

|       | $\rightarrow$ | dk1                  | Clock Input                        | Double-click to export | clk_0  |    |         |        |       |  |

| 🔶     | $\rightarrow$ | s1                   | Avalon Memory Mapped Slave         | Double-click to export | [clk1] | ÷. | 0x000x  | 0x1fff |       |  |

| +   - | $\rightarrow$ | reset1               | Reset Input                        | Double-click to export | [clk1] |    |         |        |       |  |

|       |               | 🖃 jtag_uart          | JTAG UART Intel FPGA IP            |                        |        |    |         |        |       |  |

|       | $\rightarrow$ | dk                   | Clock Input                        | Double-click to export | clk_0  |    |         |        |       |  |

| +   - | $\rightarrow$ | reset                | Reset Input                        | Double-click to export | [clk]  |    |         |        |       |  |

| ++    | $\rightarrow$ | avalon_jtag_slave    | Avalon Memory Mapped Slave         | Double-click to export | [dk]   | ÷. | 0x000x0 | 0x0007 |       |  |

|       |               | irq                  | Interrupt Sender                   | Double-click to export | [dk]   |    |         |        | ) — Ö |  |

|       |               | ⊟ sysid              | System ID Peripheral Intel FPGA IP |                        |        |    |         |        |       |  |

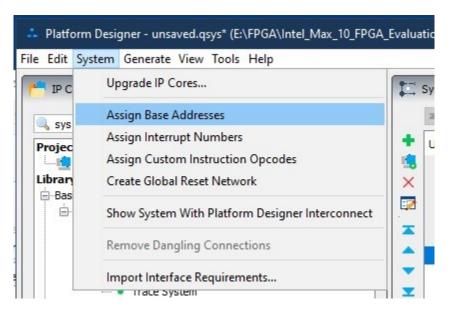

21. Let's assign a base address. From the menu, select System->Assign Base Address. This will remove a number of errors from the message box.

- 22. Finally, let's set the reset and exception vector addresses. Double-click on the nios2\_gen2\_cpu to open the configuration page.

- 23. Click on the Vectors tab.

- 24. Change the Reset vector memory drop-down to onchip\_RAM.s1.

- 25. Change the Exception vector memory drop-down to onchip\_RAM.s1.

| s        |

|----------|

| GI<br>GI |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

- 26. Click on Generate HDL...

- 27. Keep the defaults and click the Generate button.

- 28. A dialog will appear asking you to save the design, click Save.

- 29. Give the name as NIOS2.qsys and click Save.

- 30. Once the save has been completed, click Close.

- 31. The generate process kicks off. The processes should succeed, click Close.

| 🚣 Generate Completed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | × |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| AI 😢 🛆 🕕                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| <ul> <li>Info: cmd_demux: "mm_interconnect_0" instantiated altera_merlin_demultiplexer "</li> <li>Info: cmd_mux: "mm_interconnect_0" instantiated altera_merlin_multiplexer "cmd_</li> <li>Info: rsp_demux: "mm_interconnect_0" instantiated altera_merlin_demultiplexer "r:</li> <li>Info: rsp_mux: "mm_interconnect_0" instantiated altera_merlin_multiplexer "rsp_m</li> <li>Info: Reusing file E:/FPGA/Intel_Max_10_FPGA_Evaluation_Kit/NIOSii_Example/NIO:</li> <li>Info: avalon_st_adapter: "mm_interconnect_0" instantiated altera_avalon_st_adapter</li> <li>Info: error_adapter_0: "avalon_st_adapter" instantiated error_adapter "error_adapter"</li> </ul> |   |

| <ul> <li>Info: qsys-generate succeeded.</li> <li>Info: Finished: Create HDL design files for synthesis</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ť |

| Senerate: completed successfully.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| Stop Close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

- 32. Click Finish to close the design.

- 33. Quartus then reminds you to add the new design to the project. Click Ok.

- 34. In the Project Navigator, click on the drop-down and select Files.

- 35. Right-Click on Files and select Add/Remote Files in Project.

| oject Navigator |                          |           |

|-----------------|--------------------------|-----------|

| Add             | /Remove <u>F</u> iles ii | n Project |

| Add             | /Remove <u>Files</u> in  | n Project |

- A Settings NIOS2CPU page appears with Files on the left highlighted. Click the three dots, browse button for File name, and navigate to \NIOSii\_Example\NIOS2\synthesis folder.

- 37. Click on NIOS2.qip file and click open

| Name       | Date |

|------------|------|

| submodules | 7/4/ |

| NIOS2.qip  | 7/4/ |

| NIOS2.v    | 7/4/ |

|            |      |

38. Click OK to close the Settings - NIOS2CPU page. The qip file is added to the Project navigator list. Underneath are all the Verilog files that were generated by Platform Builder.

| Pro | t Navigator 📃 Files 🔹 🤍 🖵 🖉 🕱                         |

|-----|-------------------------------------------------------|

| Þ   | les                                                   |

| ÷   | NIOS2/synthesis/NIOS2.qip                             |

|     | 🗓 NIOS2/synthesis/NIOS2.v                             |

|     | NIOS2/synthesis/submodules/altera_reset_controlle     |

|     | NIOS2/synthesis/submodules/altera_reset_synchron      |

|     | Bic NIOS2/synthesis/submodules/altera_reset_controlle |

|     | NIOS2/synthesis/submodules/NIOS2_irq_mapper.sv        |

|     | NIOS2/synthesis/submodules/NIOS2_mm_intercon          |

|     | NIOS2/synthesis/submodules/NIOS2_mm_intercon          |

|     | NIOS2/synthesis/submodules/NIOS2_mm_intercon          |

| 4   | Þ                                                     |

#### 1.1.3 Create the Design Step 2: Block Diagram

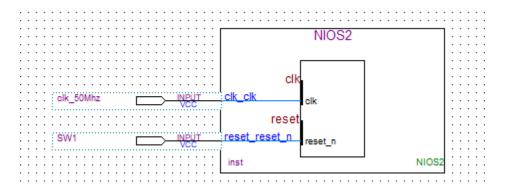

With the qip file and all the Verilog files added to the project, let's create the block diagram and complete the design.

- 1. From the menu, select New->Block Diagram/Schematic File or the icon from the toolbar. Click Ok.

- 2. The symbol window appears. Double-click on the symbol window and the symbol dialog appears.

- 3. Click on the 3 dots to open the file browser.

- 4. Browse to \NIOSii\_Example\NIOS2 folder and open the NIOS2.bsf file.

| Name        | ^ | 1 |

|-------------|---|---|

| synthesis   |   | - |

| 1 NIOS2.bsf |   | 1 |

- 5. The symbol for the NIOS2 appears. Click OK to add the symbol to the schematic.

- 6. Drag the mouse with the NIOS2 symbol to a location on the diagram and then left-click to drop it in place.

- 7. Right-click on the NIOS2 symbol and select Generate Pins for Symbol Ports.

- 8. Change the name of the clk\_clk pin to clk\_50MHz.

- 9. Change the name of the reset\_reset\_n to SW1. The SW1 switch on the evaluation kit is connected to the FPGA DEV\_CLRN pin. The circuit for SW1 is logic 1 on startup and logic0 when pressed.

- 10. Save the schematic as NIOS2CPU.bdf.

- 11. In the Task pane on the left, double-click on Fitter (Place & Route) to start the task. The analysis will take some time, and it should succeed in the end. This step helps to diagnose any errors and finds the Node Names for the pin assignments in the next step.

- 12. Once the process completes, the pin assignments need to be set. From the menu select

Assignments->Pin Planner or click on the icon from the toolbar. The analysis that was just run populated the Node Name list at the bottom of the Pin Planner dialog.

| Node Name                 | Direction | Location | I/O Bank | VREF Group | Fitter Location | I/O Standard    | R |

|---------------------------|-----------|----------|----------|------------|-----------------|-----------------|---|

|                           | Input     |          |          |            | PIN_18          | 2.5 V (default) |   |

| 🖳 altera_reserved_tdi     | Input     |          |          |            | PIN_19          | 2.5 V (default) |   |

| out altera_reserved_tdo   | Output    |          |          |            | PIN_20          | 2.5 V (default) |   |

| in altera_reserved_tms    | Input     |          |          |            | PIN_16          | 2.5 V (default) |   |

| in_ clk_50MHz             | Input     |          |          |            | PIN_28          | 2.5 V (default) |   |

| in SW1                    | Input     |          |          |            | PIN_29          | 2.5 V (default) |   |

| < <new node="">&gt;</new> |           |          |          |            |                 |                 |   |

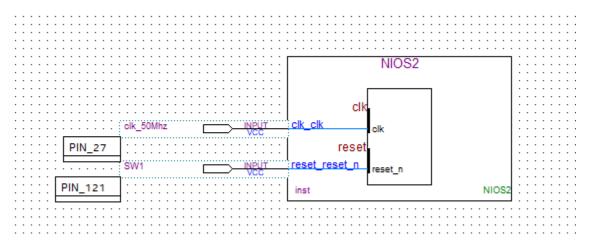

Using the board schematic, locate the pins for the SW1 and the 50Mhz clock. Set the Location values for both node names. For the MAX 10 – 10M08 Evaluation Board, these values are as follows:

| Node Name           | Location |

|---------------------|----------|

| SW1                 | PIN_121  |

| Clk_50MHz:          | PIN_27   |

| altera_reserved_tck | PIN_18   |

| altera_reserved_tdi | PIN_19   |

| altera_reserved_tdo | PIN_20   |

| altera_reserved_tms | PIN_16   |

14. Set the I/O Standard to 3.3V-LVTTL for both pins. You can see from the schematic that all of the I/O are tied to 3.3V.

Rev 1.4

### Annabooks

| Node Name                 | Direction | Location | I/O Bank | VREF Group | Fitter Location | I/O Standard    | Rese |

|---------------------------|-----------|----------|----------|------------|-----------------|-----------------|------|

| 💾 altera_reserved_tcl     | k Input   | PIN_18   | 1B       | B1_N0      | PIN_18          | 2.5 V (default) |      |

| in altera_reserved_td     | i Input   | PIN_19   | 1B       | B1_N0      | PIN_19          | 2.5 V (default) |      |

| altera_reserved_td        | o Output  | PIN_20   | 1B       | B1_N0      | PIN_20          | 2.5 V (default) |      |

| in altera_reserved_tm     | is Input  | PIN_16   | 1B       | B1_N0      | PIN_16          | 2.5 V (default) |      |

| in clk_50MHz              | Input     | PIN_27   | 2        | B2_N0      | PIN_28          | 3.3-V LVTTL     |      |

| in_ SW1                   | Input     | PIN_121  | 8        | B8_N0      | PIN_29          | 3.3-V LVTTL     |      |

| < <new node="">&gt;</new> |           |          |          |            |                 |                 |      |

15. Close the Pin Planner when finished. The diagram gets updated with the pin numbers.

16. Save the project.

**Note**: A best practice at this point would be to make a backup of the project folder. Quartus can crash unexpectedly, since it appears to be written in Java.

17. Finally, compile the design. In the Task pane, right-click on Compile and Design and select

Start from the context menu, or you can click on the symbol in the toolbar.

When the compilation hits the Assembler task, an error will appear.

| 8 | 🗴 14703 Invalid internal configuration mode for design with memory initialization |

|---|-----------------------------------------------------------------------------------|

| C | 14703 Invalid internal configuration mode for design with memory initialization   |

| ē | 2 14703 Invalid internal configuration mode for design with memory initialization |

| ē | 14703 Invalid internal configuration mode for design with memory initialization   |

| ē | 14703 Invalid internal configuration mode for design with memory initialization   |

| ē | 11702 - worldd dataanal aanfdamaataa aada fan daatam odeb warnen datedaltereten   |

| ē | 14703 Invalid internal configuration mode for design with memory initialization   |

| è | 14703 Invalid internal configuration mode for design with memory initialization   |

| ĕ | Quartus Prime Assembler was unsuccessful. 8 errors, 1 warning                     |

|   | 293001 Quartus Prime Full Compilation was unsuccessful. 10 errors, 19 warnings    |

Performing an Internet search reveals the solution on intel.com. It is a known problem for the Max 10: Error (14703): Invalid internal configuration mode for design with... (intel.com)

From this page:

Bug ID: FB: 466229;

### Description

You may see this error while compiling a custom FIFO or a RAM block in Quartus<sup>®</sup> Prime software Standard / Lite version for a MAX<sup>®</sup> 10 device.

This error is seen because MAX 10 Compact variants do not support memory initialization. If you have not provided any mif file for your custom design and still see this error in Quartus Prime software, it may be because a mif file is being inferred by the RTL coding style

#### Resolution

Signal declaration for memory\_type should be changed from

signal mem : memory\_type :=(others => (others => '0'));

to

signal mem : memory\_type;

This is to ensure that memory is not initialized and there is no compilation error in the Assembler stage.

The solution is dealing with the code, but there is a simple solution back in the onchip\_RAM confirmation page.

- 18. Open Platform Builder and open the NIOS2.qsys file.

- 19. After the design loads, double-click on the onchip\_RAM to bring up the configuration page.

- 20. Uncheck the "Initialize memory content".

| 🧏 Parameters 🛛                                        |                                                            |

|-------------------------------------------------------|------------------------------------------------------------|

| System: simpleNIOS2CPU Path: onchip                   | p_RAM                                                      |

| On-Chip Memory (RAM o<br>altera_avalon_onchip_memory2 | r ROM) Intel FPGA IP                                       |

| <ul> <li>Memory type</li> </ul>                       | ·                                                          |

| Туре:                                                 | RAM (Writable) 🗸                                           |

| Dual-port access                                      |                                                            |

| Single clock operation                                |                                                            |

| Read During Write Mode:                               | DONT CARE                                                  |

| Block type:                                           | AUTO V                                                     |

|                                                       | A010 V                                                     |

|                                                       |                                                            |

| ▼ Size                                                |                                                            |

| Enable different width for Dual-por                   | t access                                                   |

| Slave S1 Data width:                                  | 32 🗸                                                       |

| Total memory size:                                    | 8192 bytes                                                 |

| Minimize memory block usage (may                      | impact fmax)                                               |

| Read latency                                          |                                                            |

| Slave s1 Latency:                                     | 1 ~                                                        |

| Slave s2 Latency:                                     |                                                            |

|                                                       |                                                            |

| ROM/RAM Memory Protection                             |                                                            |

| Reset Request:                                        | Enabled 🗸                                                  |

| ECC Parameter                                         |                                                            |

| Extend the data width to support ECC                  | Disabled $\checkmark$                                      |

| <ul> <li>Memory initialization</li> </ul>             |                                                            |

| Initialize memory content                             |                                                            |

| Enable non-default initialization file                |                                                            |

|                                                       |                                                            |

|                                                       | hex) or select the hex file using the file browser button. |

| User created initialization file:                     | onchin mem.hex                                             |

- 21. Click on Generate HDL...

- 22. Click Close after the save process completes.

- 23. Click Close after the generation completes.

- 24. Click Finish to close Platform Builder.

- 25. The Quartus reminder appears. Click Close.

- 26. Compile the design again, and this time it should be successful.

| Flow Summary                       |                                             |

|------------------------------------|---------------------------------------------|

| < <filter>&gt;</filter>            |                                             |

| Flow Status                        | Successful - Sat Jul 2 16:33:40 2022        |

| Quartus Prime Version              | 21.1.0 Build 842 10/21/2021 SJ Lite Edition |

| Revision Name                      | SimpleNIOS2                                 |

| Top-level Entity Name              | SimpleNIOS2                                 |

| Family                             | MAX 10                                      |

| Device                             | 10M08SAE144C8G                              |

| Timing Models                      | Final                                       |

| Total logic elements               | 3,187 / 8,064 ( 40 % )                      |

| Total registers                    | 1846                                        |

| Total pins                         | 2 / 101 ( 2 % )                             |

| Total virtual pins                 | 0                                           |

| Total memory bits                  | 128,512 / 387,072 ( 33 % )                  |

| Embedded Multiplier 9-bit elements | 6 / 48 (13 %)                               |

| Total PLLs                         | 0/1(0%)                                     |

| UFM blocks                         | 0/1(0%)                                     |

| ADC blocks                         | 0/1(0%)                                     |

### 1.1.4 **Program the Board**

With the design compiled, we can now test the design on the board.

1. Connect the board and the programming cable together per the cable instructions.

**Note**: The MAX 10 – 10M08 Evaluation Kit doesn't come with a programming cable or built-in JTAG USB Blaster II. You will have to use either the USB Blaster II or EthernetBlaster II external cables. The EthernetBlaster II was used. DHCP setup was not working, so a direct Ethernet cable connection was made between a PC and the EthernetBlaster II. Set the static IP for the PC network card to 198.162.0.1. Access the EthernetBlaster II via a browser and then change the IP to a static IP that matches the network. The new IP address was used as the Server name. Your experience might be different.

- 2. Power on the board and the programming cable box.

- 3. In Quartus Prime, from the Task pane, right-click on Program Device (Open Programmer)

and select Open from the context menu or click on the icon on the toolbar.

The Programmer dialog appears, click on the "Hardware Setup" button.

5. Click the Add hardware button, select the Hardware type, and fill in any remaining information, and click OK.

| Hardware Settings                           | JTAG S  | ettings     |        |                       |

|---------------------------------------------|---------|-------------|--------|-----------------------|

| Select a programmin<br>hardware setup appli |         |             |        | ces. This programming |

| Currently selected ha                       | rdware: | No Hardware |        | •                     |

| Hardware frequency<br>Add Hardware          | 2       |             | ×      | ٢                     |

| Hardware type:                              | Ethern  | etBlaster   | •      | Add Hardware          |

| Port:                                       |         |             | *      | Remove Hardware       |

| Baud rate:                                  |         |             | T      |                       |

| Server name:                                |         |             | *      |                       |

| Server port:                                | 1309    |             |        |                       |

| Server password:                            |         |             |        |                       |

| Auto Detect                                 |         | ок          | Cancel |                       |

6. The tool allows you to connect to a number of programming cables. We need to select the one for our board. In the "Currently selected hardware", click the drop-down, select the hardware cable for the board, and click Close when finished

| Hardware Settings JTAG S                                       | ettings |                  |                   |                      |

|----------------------------------------------------------------|---------|------------------|-------------------|----------------------|

| Select a programming hardwar<br>hardware setup applies only to |         |                  |                   | es. This programming |

| Currently selected hardware:                                   | Etherne | tBlasterII on 19 | 92.168.1.198 [Eth | ernetBlasterII] 🔹    |